# DIGITAL ELECTRONICS

**Theory and Experiments**

A

NEW AGE INTERNATIONAL PUBLISHERS

Copyright © 2002, New Age International (P) Ltd., Publishers Published by New Age International (P) Ltd., Publishers

First Edition: 2002 Reprint: 2006

#### All rights reserved.

No part of this book may be reproduced in any form, by photostat, microfilm, xerography, or any other means, or incorporated into any information retrieval system, electronic or mechanical, without the written permission of the copyright owner.

ISBN:81-224-1346-3

Rs. 165.00

45678910

C-06-01-553

Printed in India at A.P. Offset, Delhi.

PUBLISHING FOR ONE WORLD

NEW AGE INTERNATIONAL (P) LIMITED, PUBLISHERS (formerly Wiley Eastern Limited)

4835/24, Ansari Road, Daryaganj, New Delhi - 110002

Visit us at www.newagepublishers.com

# **CONTENTS**

#### PREFACE

| 1. | LOGIC SYSTEMS                         | 1  |

|----|---------------------------------------|----|

|    | 1.1. Introduction                     | 1  |

|    | 1.2. Logic Gates                      | 1  |

|    | 1.3. Boolean Algebra                  | 2  |

|    | 1.4. Logic Polarity                   | 5  |

|    | 1.5. Logic Trainer                    |    |

| 2. | LOGIC FAMILIES                        | 8  |

|    | 2.1. Introduction                     | 8  |

|    | 2.2. Numbering System for Digital ICs | 8  |

|    | 2.3. TTL Characteristics              | 10 |

|    | 2.4. TTL Sub-families                 | 14 |

|    | 2.5. MOS Family Characteristics       | 17 |

|    | 2.6. CMOS Sub-families                | 19 |

|    | 2.7. Integrated Circuit Packaging     | 20 |

| 3. | INVERTERS : BUFFERS                   | 23 |

|    | 3.1. Introduction                     | 23 |

|    | Experiment 3.1: Inverters             | 24 |

| 4. | AND : OR GATES                        | 27 |

|    | 4.1. Introduction                     | 27 |

|    | 4.2. AND Gates                        | 27 |

|    | Experiment 4.1: Two-Input AND Gate    | 28 |

|    | Experiment 4.2: Three-Input AND Gate  | 32 |

|    | 4.3. OR Gates                         | 34 |

|    | Experiment 4.3: Two-Input OR Gate     | 35 |

| 5. | NAND : NOR GATES                      | 39 |

|    | 5.1. Introduction                     | 39 |

|    | 5.2. NAND Gate                        | 39 |

|    | Experiment 5.1: Three-Input NAND Gate | 40 |

|    | 5.3. NOR Gates                        | 44 |

|    | Experiment 5.2 - Two-Input NOR Gate   | 44 |

#### x Contents

|    | 5.4.        | NOR Logic                                                            | 46 |

|----|-------------|----------------------------------------------------------------------|----|

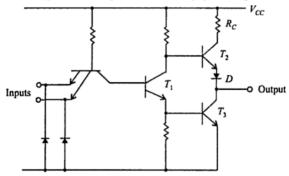

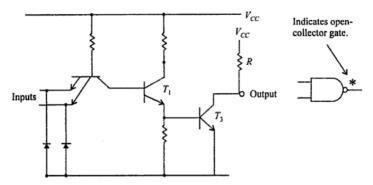

|    | 5.5.        | TTL Output Configurations                                            | 47 |

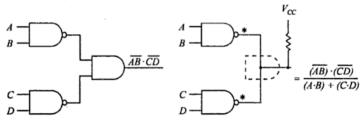

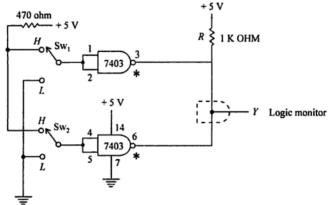

|    |             | Experiment 5.3: Open-Collector Inverters                             | 48 |

|    |             | Experiment 5.4: Open-Collector NAND Gates                            | 50 |

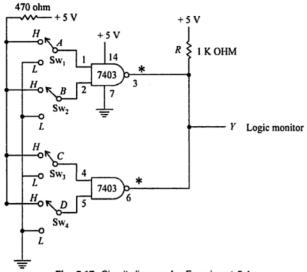

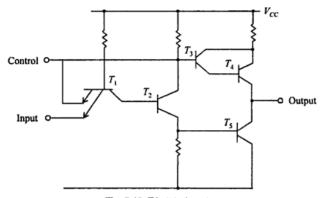

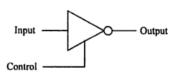

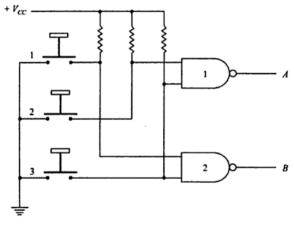

|    |             | Experiment 5.5 : Tri-State Buffer                                    | 54 |

| 6. | XOF         | R : XNOR GATES                                                       | 58 |

|    | 6.1.        | Introduction                                                         | 58 |

|    | 6.2.        | Exclusive-OR (XOR) Gate                                              | 58 |

|    |             | Experiment 6.1: Two-Input XOR Gate                                   | 59 |

|    |             | Experiment 6.2: Three-Input XOR Gate                                 | 61 |

|    | 6.3.        | Exclusive-NOR (XNOR) Gate                                            | 62 |

| 7. | INT         | ERFACING TTL: CMOS GATES                                             | 65 |

|    | 7.1.        | Introduction                                                         | 65 |

|    | 7.2.        | CMOS to CMOS Interface                                               | 65 |

|    | 7.3.        | TTL to TTL Interface                                                 | 66 |

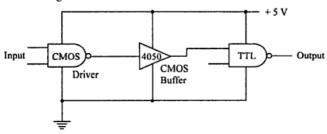

|    | 7.4.        | CMOS to TTL Interface                                                | 66 |

|    | 7.5.        | TTL to CMOS Interface                                                | 67 |

|    |             | Experiment 7.1: Interfacing TTL Driver to CMOS                       |    |

|    |             | Load with a pull-up Resistor                                         | 69 |

|    | <u>7.6.</u> | Interfacing TTL Driver to External Loads                             | 70 |

|    |             | Experiment 7.2: Interfacing TTL Driver to LEDs                       | 71 |

|    |             | Experiment 7.3: TTL Lamp Drivers                                     | 72 |

|    |             | Experiment 7.4 : TTL Driver — Load Interface (Limited Drive Current) | 73 |

|    |             | Experiment 7.5 : CMOS to Lamp Interface                              | 75 |

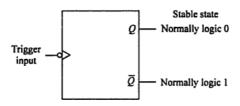

| 8. | BIS         | TABLE MULTIVIBRATORS (FLIP-FLOPS)                                    | 77 |

|    | 8.1.        | Introduction                                                         | 77 |

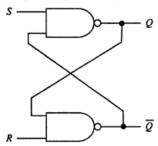

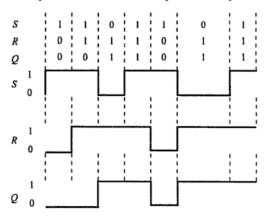

|    | 8.2.        | RS NAND Latch                                                        | 77 |

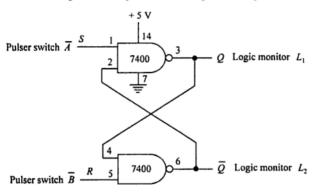

|    |             | Experiment 8.1 : RS NAND Latch                                       | 79 |

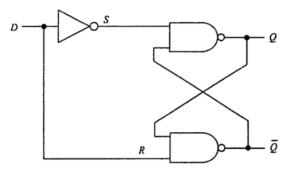

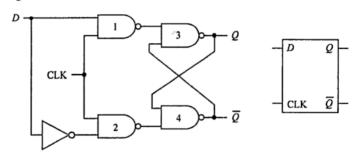

|    | 8.3.        | D Latch                                                              | 81 |

|    | 8.4.        | Clocked D Latch                                                      | 82 |

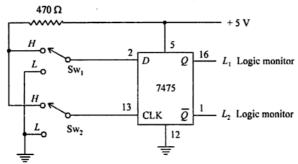

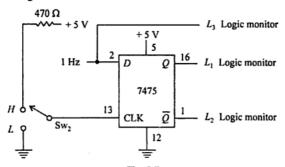

|    |             | Experiment 8.2 : Clocked D Latch                                     | 82 |

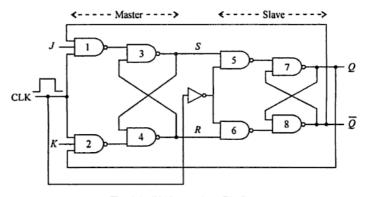

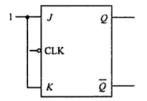

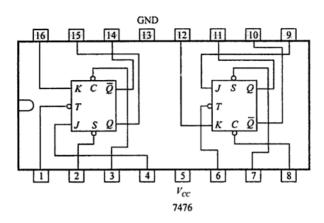

|    | 8.5.        | JK Flip-Flop (Level-clocked)                                         | 84 |

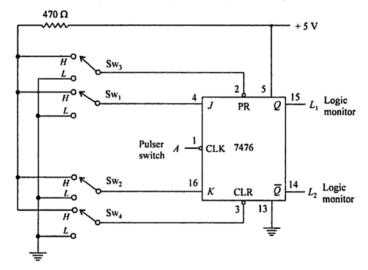

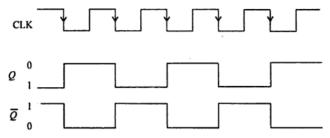

|    |             | Experiment 8.3 : JK Flip-Flop                                        | 86 |

|    |             | Experiment 8.4 : JK Flip-Flop                                        | 89 |

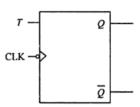

|    | 8.6.        | T Flip-Flop                                                          | 91 |

ŧ

| 9.         | ASTABLE AND MONOSTABLE MULTIVIBRATORS                 | 93  |

|------------|-------------------------------------------------------|-----|

|            | 9.1. Introduction                                     | 93  |

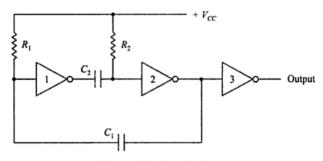

|            | 9.2. TTL Clock Oscillator                             | 94  |

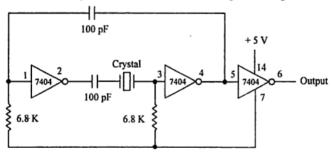

|            | 9.3. Crystal-Controlled Clock Oscillator              | 95  |

|            | Experiment 9.1: Crystal-controlled Oscillator         | 95  |

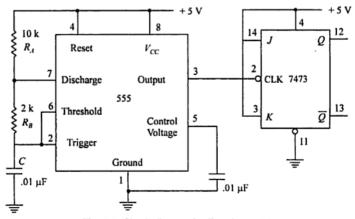

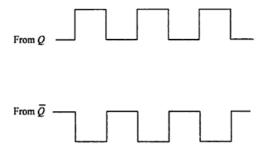

|            | Experiment 9.2 : Square wave Generator                | 96  |

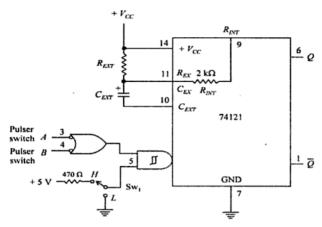

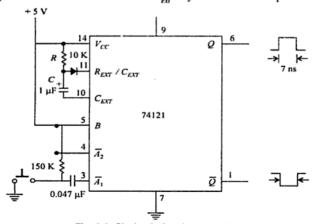

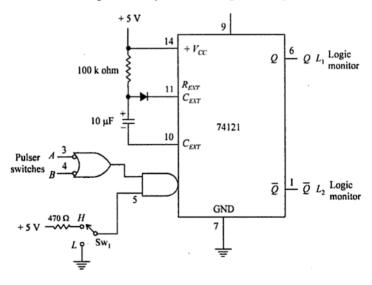

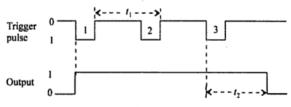

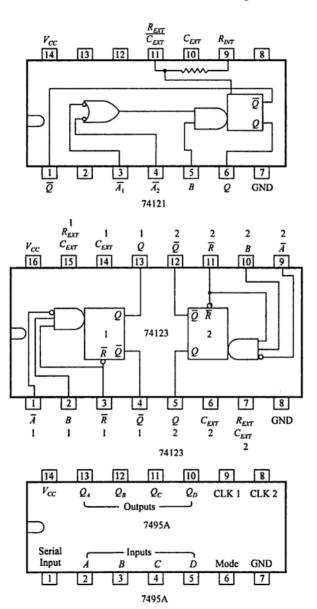

|            | 9.4. Non-Retriggerable Monostable : IC 74121          | 97  |

|            | Experiment 9.3: Non-Retriggerable Monostable:         |     |

|            | IC 74121                                              | 100 |

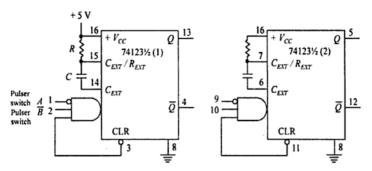

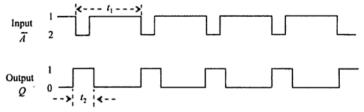

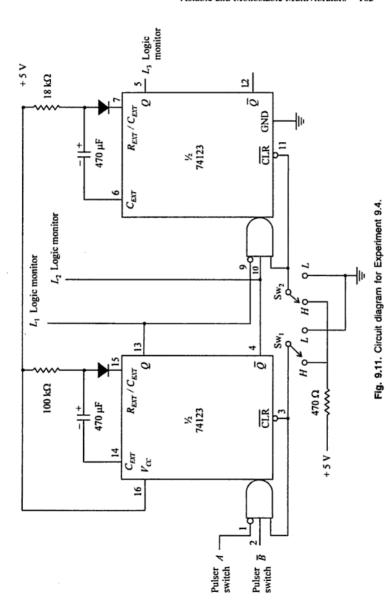

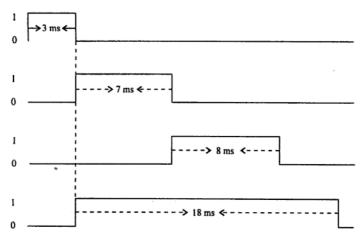

|            | 9.5. Retriggerable Monostable : IC 74123              | 102 |

|            | Experiment 9.4: Retriggerable Monostable:             |     |

|            | IC 74123                                              | 104 |

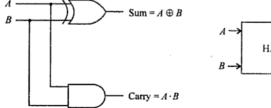

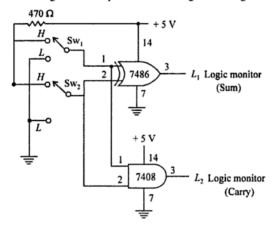

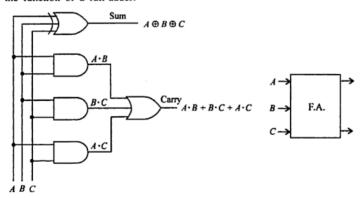

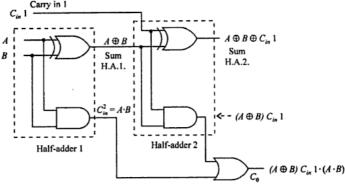

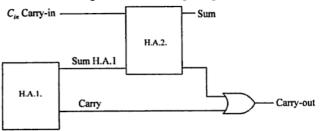

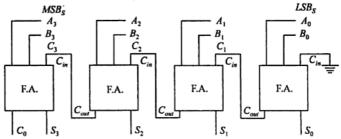

| <u>10.</u> | ARITHMETIC LOGIC CIRCUITS                             | 109 |

|            | 10.1. Introduction                                    | 109 |

|            | 10.2. Addition                                        | 109 |

|            | Experiment 10.1: Half-Adder                           | 111 |

|            | 10.3. Full-Adder                                      | 112 |

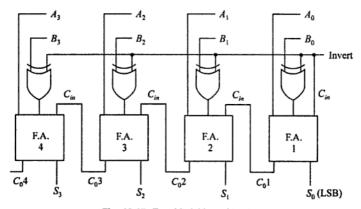

|            | 10.4. Four-bit Adder                                  | 114 |

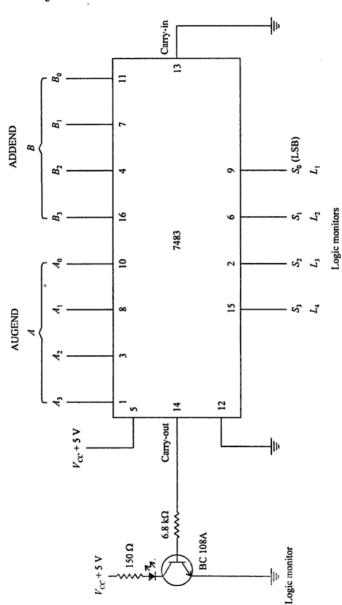

|            | Experiment 10.2: Four-bit Adder                       | 115 |

|            | 10.5. Binary Subtraction                              | 117 |

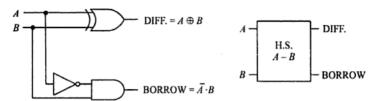

|            | 10.5.1. Half-Subtracter                               | 118 |

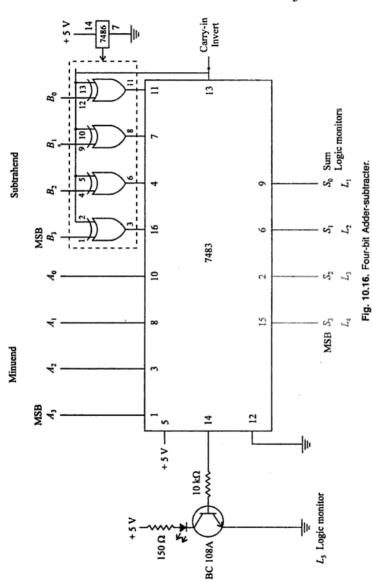

|            | 10.5.2. 2's Complement Adder-Subtracter               | 119 |

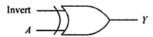

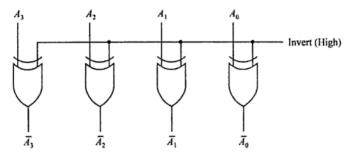

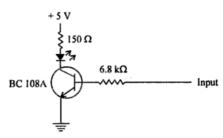

|            | Experiment 10.3: Four-bit Adder-Subtracter            | 121 |

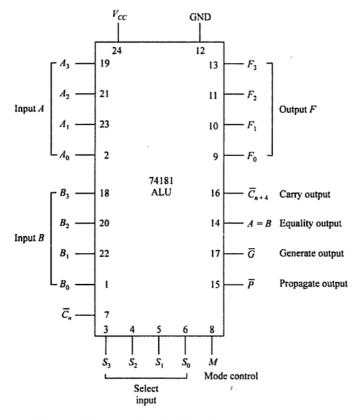

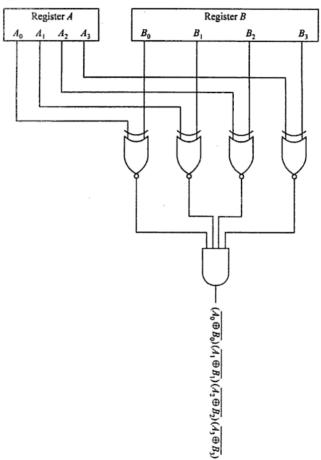

|            | 10.6. Arithmetic Logic Unit: IC 74181                 | 124 |

|            | Experiment 10.4: Arithmetic Logic Unit                | 129 |

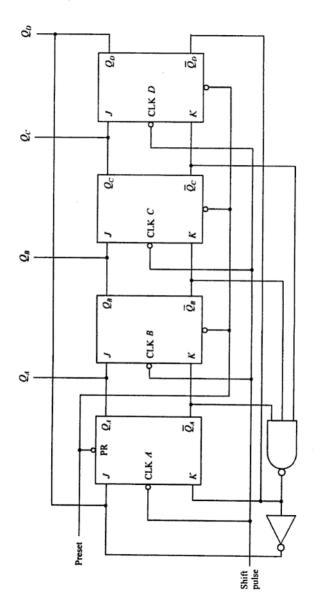

| 11.        | SHIFT REGISTERS                                       | 131 |

|            | 11.1. Introduction                                    | 131 |

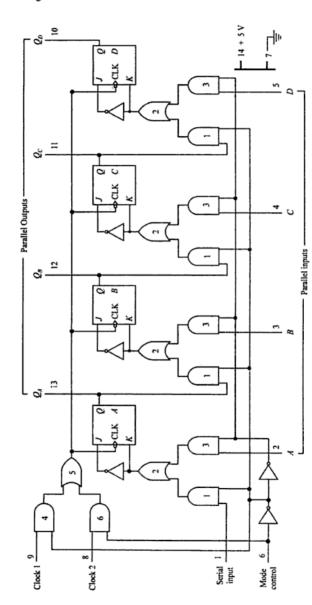

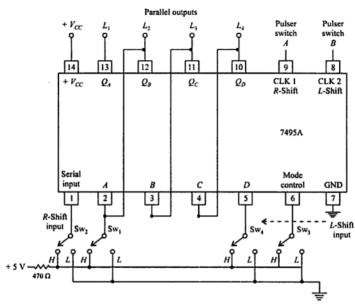

|            | 11.2. Universal Shift Register: IC 7495A              | 131 |

|            | Experiment 11.1: Shift Register: IC 7495A             | 134 |

|            | Experiment 11.2 : Right-Shift / Left-Shift Function : |     |

|            | IC 7495A                                              | 136 |

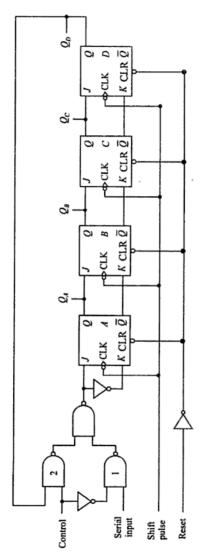

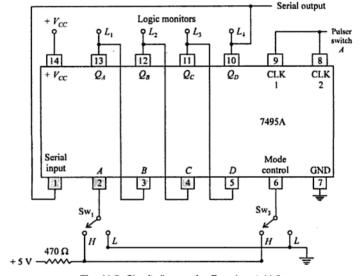

|            | 11.3. Recirculating Shift Register                    | 138 |

|            | Experiment 11.3: Recirculating Shift Register:        |     |

|            | IC 7495A                                              | 140 |

| 12.        | COUNTERS                                              | 142 |

|            | 12.1. Introduction                                    | 142 |

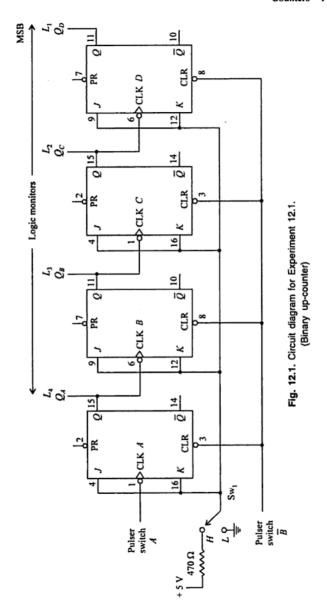

|            | 12.2. Binary Ripple Up-counter                        | 142 |

|            | Europiniant 12.1 . Dinom: Un counter                  | 144 |

| 145  |

|------|

| 146  |

| 148  |

| 151  |

|      |

| 154  |

|      |

| 155  |

| 156  |

| 156  |

| 158  |

| 159  |

| 161  |

| 161  |

| 163  |

| 164  |

| _165 |

| 168  |

| 173  |

| 173  |

| 173  |

| 174  |

| 174  |

| 177  |

| 178  |

|      |

| 179  |

| 182  |

| 182  |

| 182  |

| 184  |

| 186  |

| 189  |

| 190  |

| 190  |

| 172  |

| 192  |

|      |

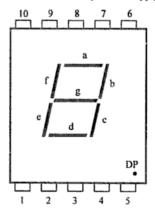

| 15. | SEVEN-SEGMENT LED DISPLAY                       | 196        |  |

|-----|-------------------------------------------------|------------|--|

|     | 15.1. Introduction                              | 196        |  |

|     | 15.2. Single Digit Display                      | 196        |  |

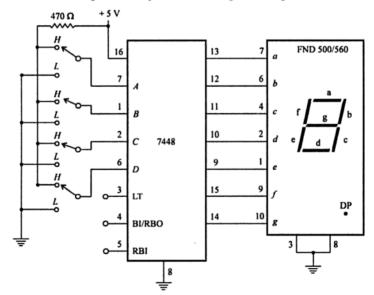

|     | 15.3. BCD-to-Seven-Segment Decoder Driver       | 198        |  |

|     | Experiment 15.1: Seven-Segment LED Display      |            |  |

|     | with IC 7447A                                   | 201        |  |

|     | Experiment 15.2: Seven-Segment LED Display      |            |  |

|     | with IC 7448                                    | 203        |  |

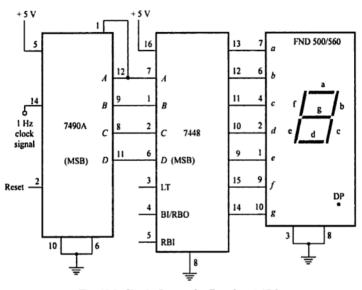

|     | Experiment 15.3: Decade Counter with            |            |  |

|     | Seven-Segment Display                           | 204        |  |

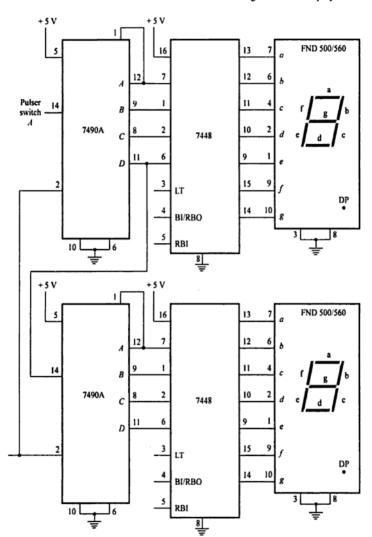

|     | Experiment 15.4: Counter with Double-digit      | 201        |  |

|     | Capability                                      | 206        |  |

|     | 15.4. Digital Display with Memory               | 209        |  |

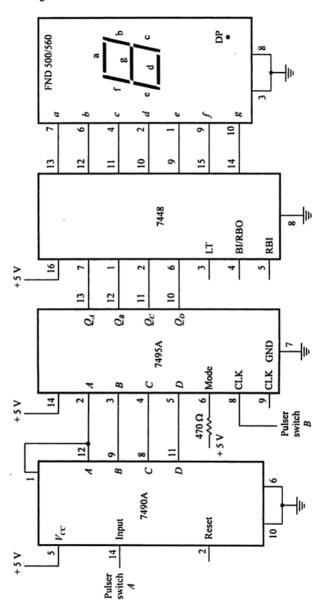

|     | Experiment 15.5 : Counter Display using         | 200        |  |

|     | Memory Register                                 | 209        |  |

| 16. | SEMI-CONDUCTOR MEMORY                           | 212        |  |

|     | 16.1. Introduction                              | 212        |  |

|     | 16.2. Random Access Memory (RAM): IC 7489       | 212        |  |

|     | Experiment 16.1: Random Access Memory (RAM):    |            |  |

|     | IC 7489                                         | 219        |  |

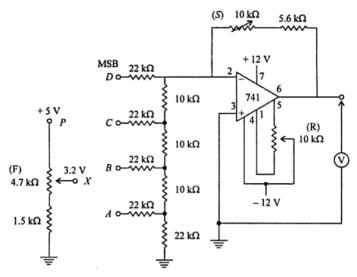

| 17. | ANALOG/DIGITAL & DIGITAL/ANALOG CONVERSION      | 223        |  |

|     | 17.1. Introduction                              | 223        |  |

|     | 17.2. Summing Network D/A Converter             | 223        |  |

|     | Experiment 17.1: Digital/Analog Converter       | 224        |  |

|     | 17.3. Ladder Network (D/A Converter)            | 226        |  |

|     | Experiment 17.2: Ladder Network (D/A Converter) | 227        |  |

|     | 17.4. Analog/Digital Converter : ADC 0804       | 229        |  |

|     | Experiment 17.3: A/D Converter: ADC 0804        | 230        |  |

|     |                                                 |            |  |

|     | APPENDICES                                      |            |  |

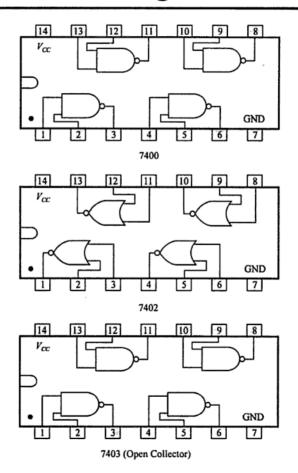

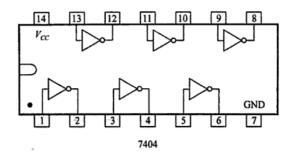

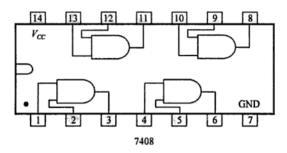

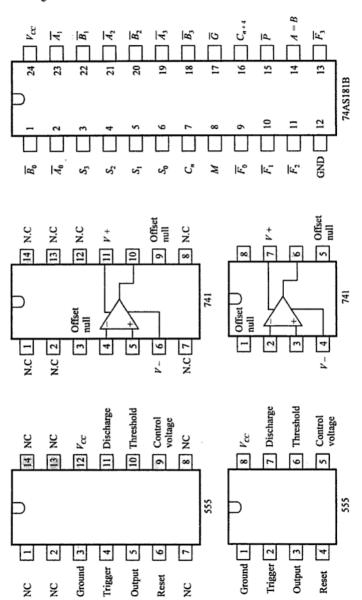

| 1.  | Pin Connections for Integrated Circuits         | 237        |  |

| 2.  | Equipment and Parts Required for Experiments    | 245        |  |

|     | Completed Experimental Tables                   | 247        |  |

| 4.  | Answers to Selected Problems                    | 257        |  |

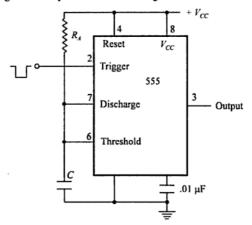

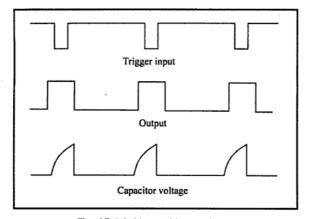

| 5.  | 555 Timer                                       |            |  |

| 6.  | Logic Gates : Implementation : Truth Tables     |            |  |

| 7.  |                                                 |            |  |

| 8.  |                                                 |            |  |

| 9.  | -                                               |            |  |

| 10. | Boolean Algebra                                 | 279<br>281 |  |

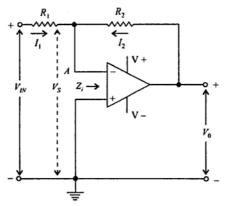

| 11. | Operational Amplifier                           | 283        |  |

| 12. |                                                 | 294        |  |

|     | Index                                           | 303        |  |

## LIST OF EXPERIMENTS

| <u>S. No.</u> | Experiment No.                                     |     |

|---------------|----------------------------------------------------|-----|

| 1             | 3.1. Inverters                                     | 24  |

| 2.            | 4.1. Two-Input AND Gate: IC 7408                   | 28  |

| 3.            | 4.2. Three-Input AND Gate                          | 32  |

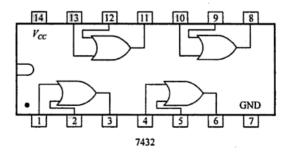

| 4.            | 4.3. Two-Input OR Gate: IC 7432                    | 35  |

| 5.            | 5.1. Three-Input NAND Gate                         | 40  |

| 6.            | 5.2. Two-Input NOR Gate: IC 7402                   | 44  |

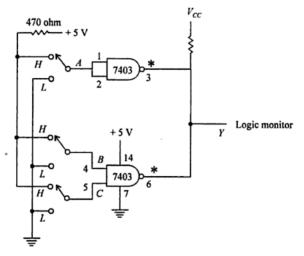

| 7.            | 5.3. Open-Collector Inverters: IC 7403             | 48  |

| 8.            | 5.4. Open-Collector NAND Gates: IC 7403            | 50  |

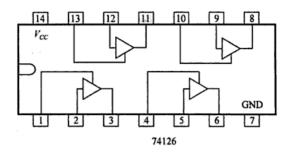

| 9             | 5.5. Tri-State Buffer : IC 74126                   | 54  |

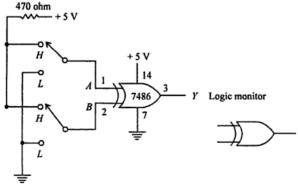

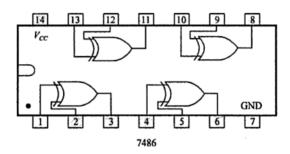

| 10.           | 6.1. Two-Input XOR Gate: IC 7486                   | 59  |

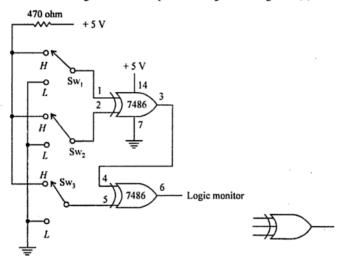

| 11.           | 6.2. Three-Input XOR Gate: IC 7486                 | 61  |

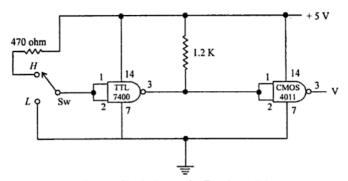

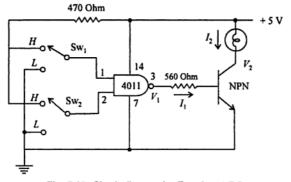

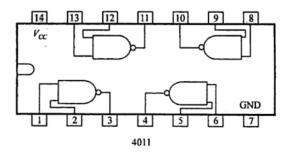

| 12.           | 7.1. Interfacing TTL Driver to CMOS Load           |     |

|               | with a pull up Resistor : IC 4011                  | 69  |

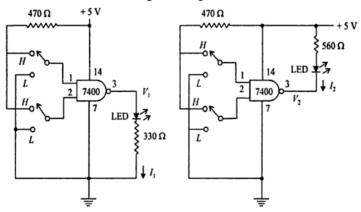

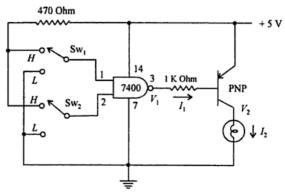

| 13.           | 7.2. Interfacing TTL Drivers to LEDs: IC 7400      | 71  |

| 14.           | 7.3. TTL Lamp Drivers : IC 7400                    | 72  |

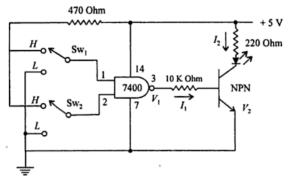

| 15.           | 7.4. TTL Driver-Load Interface: IC 7400            |     |

|               | (Limited Drive Current)                            | 73  |

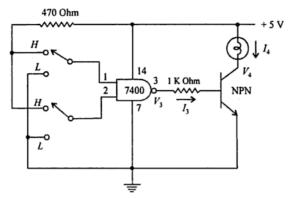

| <u>16.</u>    | 7.5. CMOS to Lamp Interface : IC 4011              | 75  |

| 17            | 8.1. RS NAND Latch: IC 7400                        | 79  |

| 18            | 8.2. Clocked D-Latch : IC 7475                     | 82  |

| 19.           | 8.3. JK Flip-Flop: IC 7476                         | 86  |

| 20.           | 8.4. JK Flip-Flop : IC 7476                        | 89  |

| 21.           | 9.1. Crystal-controlled Oscillator : IC 7404       | 95  |

| 22.           | 9.2. Square-wave Generator: IC 555, IC 7473        | 96  |

| 23.           | 9.3. Non-Retriggerable Monostable : IC 74121       | 100 |

| 24.           | 9.4. Retriggerable Monostable : IC 74123           | 104 |

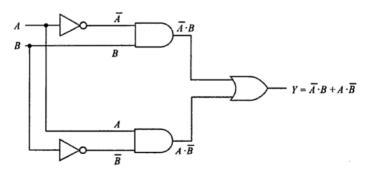

| 25.           | 10.1. Half-Adder : IC 7408, IC 7486                | 111 |

| 26.           | 10.2. Four-bit Adder : IC 7483                     | 115 |

| <u>27.</u>    | 10.3. Four-bit Adder-Subtracter : IC 7483, IC 7486 | 121 |

| 28.           | 10.4. Arithmetic Logic Unit: IC 74181              | 129 |

| 29.           | 11.1. Shift Register : IC 7495A                    | 134 |

| 30.           | 11.2. Right-Shift Left-Shift Function: IC 7495A    | 136 |

| 31.           | 11.3. Recirculating Shift Register : IC 7495A      | 140 |

| Con | tents | X١ |

|-----|-------|----|

|     |       |    |

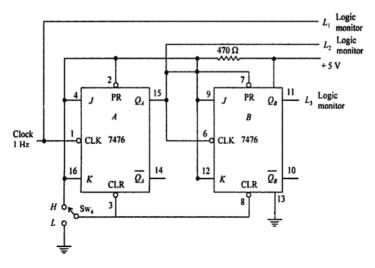

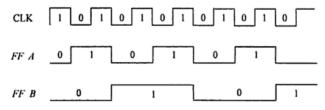

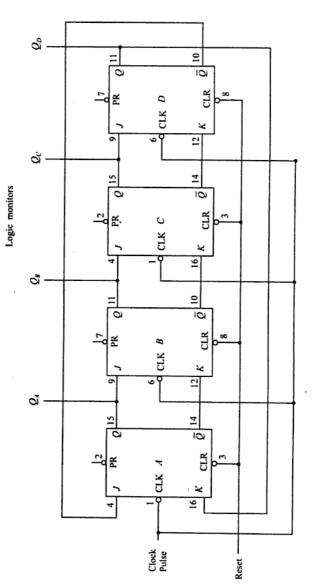

| 32.         | 12.1.  | Binary Up-Counter: IC 7476                  | 144 |

|-------------|--------|---------------------------------------------|-----|

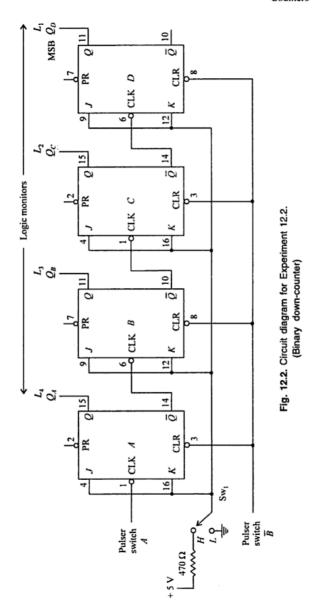

| 33.         | 12.2.  | Binary Down-Counter: IC 7476                | 146 |

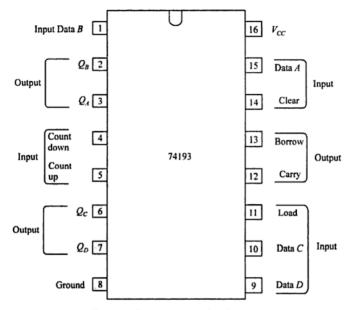

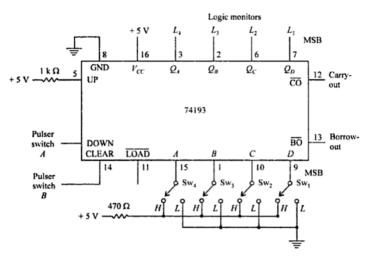

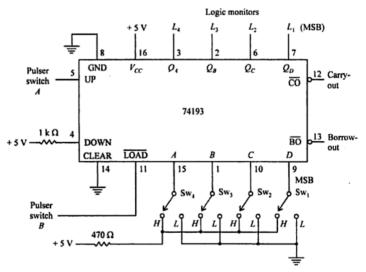

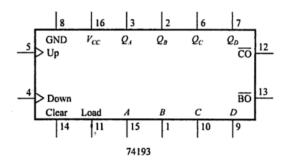

| 34.         | 12.3.  | Up-Down Counter: IC 74193                   | 151 |

| 35.         | 12.4.  | Presettable Counter Function :              |     |

|             |        | IC 74193 (Up-counting Mode)                 | 154 |

| <u> 36.</u> | 12.5.  | Presettable Counter Function :              |     |

|             |        | IC 74193 (Down-counting Mode)               | 155 |

| <u>37.</u>  | 12.6.  | Modulo Counter using: IC 74193              | 156 |

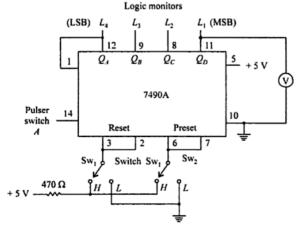

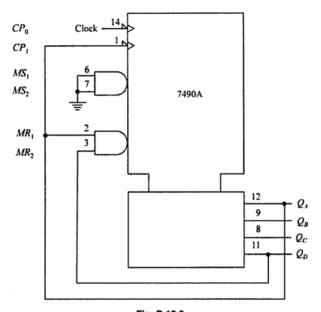

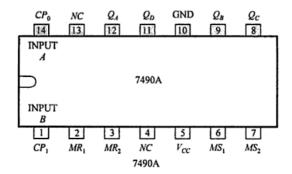

| 38.         | 12.7.  | BCD Counter: IC 7490A                       | 159 |

| <u>39.</u>  | 12.8.  | Divide-By-Ten Counter : IC 7490A            | 161 |

| <u>40.</u>  | 12.9.  | Ring Counter: IC 7495A                      | 164 |

| 41.         | 12.10. | Johnson Counter: IC 7495A, IC 7404          | 168 |

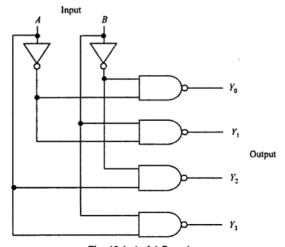

| 42.         | 13.1.  | BCD-to-Decimal Decoder : IC 7442            | 174 |

| 43.         | 13.2.  | Decimal Priority Encoder : IC 74147         | 179 |

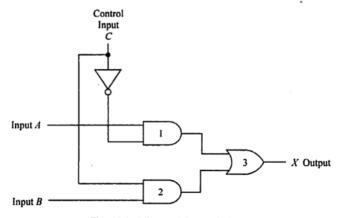

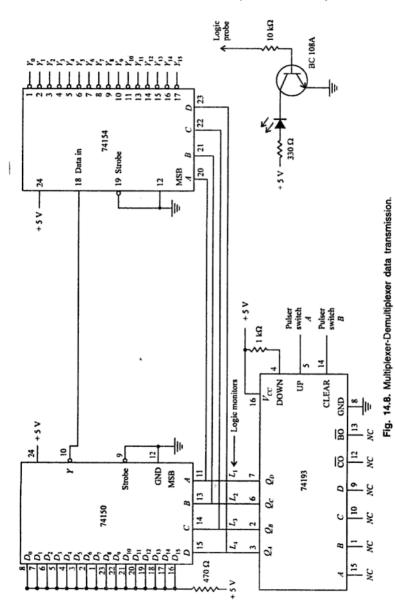

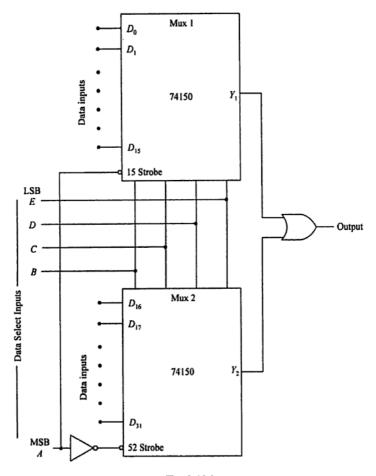

| 44.         | 14.1.  | Multiplexer : IC 74150                      | 186 |

| 45.         | 14.2.  | Multiplexer-Demultiplexer Data Transmission |     |

|             |        | (ICs 74150, 74154, 74193)                   | 192 |

| 46.         | 15.1.  | Seven-Segment LED Display : IC 7447A        | 201 |

| 47.         | 15.2.  | Seven-Segment LED Display: IC 7448          | 203 |

| 48.         | 15.3.  | Decade Counter with Seven-Segment Display   | 204 |

| 49.         | 15.4.  | Counter with Double-Digit Capability        | 206 |

| 50.         | 15.5.  | Counter Display using Memory Register       |     |

|             |        | (ICs 7448, 7490A, 7495A)                    | 209 |

| 51.         | 16.1.  | Random Access Memory: IC 7489               | 219 |

| 52.         | 17.1.  | Digital/Analog Converter : IC 741           | 224 |

| 53.         | 17.2.  | Ladder Network (D/A Converter) : IC 741     | 227 |

| E 4         | 17.2   | A.D. Composition v. IC. A.D.C. 0004         | 220 |

# LOGIC SYSTEMS

#### 1.1. INTRODUCTION

The binary number system can be visualized as one having two discrete states. The term binary can represent any two-state device. The two states of a binary system are designated by symbols 0 and 1. For instance, you can represent the OFF and ON states of an electrical circuit by these two symbols. If 1 represents the ON state; 0 can represent the OFF state. It really depends on the convention we choose to adopt. We can also adopt 0 for the ON state and 1 for the OFF state.

In digital electronics the binary system of representation is used mainly because the two states in the binary system are very specific and convenient to adopt. We can also represent voltage levels in the binary system. Consider the following representation of voltage levels in the binary system:

```

0 volt : Binary 0

and + 5 volt : Binary 1

or

0 volt : Binary 1

+ 5 volt : Binary 0

```

It is really a matter of convention that you choose to adopt. The binary designation of voltage levels can also be used to represent logic levels and in fact it is the common practice. For instance we can refer to +5 V as logic 1 level and 0 V as logic 0 level. However, normally logic 1 level is considered to be the more positive of the two levels and the logic 0 level is assigned to the more negative of the two levels. This convention is referred to as positive logic. In negative logic the more negative of the two levels is designated as the logic 1 level. We will come back to the topic of logic polarity a little later.

#### 1.2. LOGIC GATES

Logic gates are used in digital circuits for the purpose of logical decisions. There are the following basic types of gates for which symbols are given in Table 1.1.

NOT gate or Inverter AND gate NAND gate OR gate NOR gate

You can visualize a logic gate as a two-state logic element. In other words, you may say that its output may be either low or high, that is logic 0 or logic 1. The state of its output depends on its functional type, as well as on the present condition of its inputs. Logic gates do not possess memory and therefore, the output changes with the change of input levels. We will, at a later stage, consider flip-flops which are combinations of logic gates and possess memory.

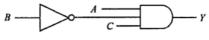

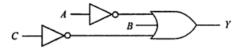

Some other gates are derived from these basic gates. The NOT gate or Inverter is used to invert or complement the logic level. For instance, if the logic level is high or 1, it can complement it to 0 as the complement of 1 is 0. If the logic level is 0, it can complement it to 1, since  $\overline{0} = 1$  (it is read as Not 0 = 1). An example of complementation is seen in the NAND gate which is a contraction for NOT-AND. In other words, if the output of an AND gate is complemented by using an Inverter, it becomes a NAND gate. Similarly, the NOR gate is a contraction for NOT-OR. The OR gate functions as a NOR gate if its output is complemented.

The Inverter has a single input and a single output. However, the other gates may have two or more inputs and a single output. As there are only two logic levels in digital circuits, the output of a gate is either high (logic 1) or low (logic 0) in positive logic. The several inputs to a logic gate may all have different logic levels; but that depends on the functions being assigned to the various inputs.

Three methods are available to us for describing and predicting the input/ output properties of gates and of combinations of gates. These are:

- \* Boolean algebra

- \* Truth tables

- and \* Timing diagrams

We will take up the Boolean algebra first and see how the input/output relationship can be expressed in an equation form.

#### 1.3. BOOLEAN ALGEBRA

Boolean expressions consist of variables like A, B, C etc., which can have either of the two values 0 or 1, constants and operators. The result of a Boolean function is either 0 or 1. For instance,  $A \cdot B$  (read as A and B) can either be 1 or 0. Boolean algebra uses symbols which represent operators. The symbols have been summarized below:

Table 1.1

| <u></u> | Device                 | Abbreviation                       | Symbol                                                             |

|---------|------------------------|------------------------------------|--------------------------------------------------------------------|

| 1.      | Inverter               | $Y = \overline{A}$                 | AY                                                                 |

| 2.      | Buffer                 | Y = A                              | А — У                                                              |

| 3.      | AND Gate               | AND $Y = A \cdot B$                | A                                                                  |

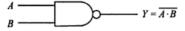

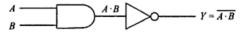

| 4.      | NAND Gate              | NAND $Y = \overline{A \cdot B}$    | A                                                                  |

| 5.      | OR Gate                | OR $Y = A + B$                     | А Y                                                                |

| 6.      | NOR Gate (Not OR Gate) | NOR $Y = \overline{A + B}$         | А Y                                                                |

| 7.      | Exclusive – OR Gate    | $XOR$ $Y = A \oplus B$             | A                                                                  |

| 8.      | Exclusive - NOR Gate   | $XNOR$ $Y = \overline{A \oplus B}$ | A                                                                  |

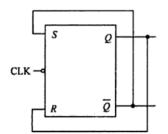

| 9.      | Set-Reset Flip-Flop    | FF                                 | $\frac{\begin{bmatrix} S & Q \\ R & \overline{Q} \end{bmatrix}}{}$ |

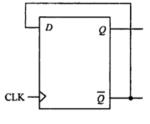

| 10.     | J K Flip-Flop          |                                    | J S Q<br>T C Q                                                     |

| 11.     | Schmitt Trigger        |                                    | A                                                                  |

- \* INVERT (Complement) uses a bar over a variable.

\( \overline{A} \) is read as 'Not A'. It represents the complement of A.

- \* AND is represented by (·) or (×) between variables. It is written as A·B or more simply AB. If A and B are the two inputs of an AND gate, its output is AB.

- NAND is represented by a bar over the complemented variables. For instance, the output of a 2-input NAND gate can be stated as AB.

- \* OR is represented by a + (plus) sign between variables. If the two inputs of an OR gate are A and B, its output will be A + B (read as A or B).

- \* NOR is represented by a bar over both the variables which are ORed. For instance, the NOR output of a 2-input NOR gate can be written as  $\overline{A+B}$ .

- XOR (Exclusive OR) output of a 2-input XOR gate is written as A ⊕ B.

- \* XNOR (Exclusive NOR) output of a 2-input XNOR gate is written as A⊕B.

The following examples will enable you to understand how Boolean expressions should be read :

| $A \cdot B$                       | A and $B$        |

|-----------------------------------|------------------|

| $\overline{A} \cdot B$            | Not $A$ and $B$  |

| $A \cdot \overline{B}$            | A and Not $B$    |

| $\overline{A} \cdot \overline{B}$ | Not A and Not B  |

| A + B                             | $A 	ext{ or } B$ |

| $\overline{A} + B$                | Not $A$ or $B$   |

| $A + \overline{B}$                | A or Not B       |

| $\overline{A} + \overline{B}$     | Not A or Not B   |

| A = B                             | A equals $B$     |

When designing logic circuits the normal practice is to draw up a truth table and then the required Boolean expression. It is necessary to reduce the Boolean expression to the simplest form so that the design can be implemented with the smallest number of gates. For this exercise the laws of Boolean algebra are found very useful. These laws have been summarized in Appendix 10.

#### Truth Table

Just as Boolean algebra is found useful in describing the input/output relationship of logic systems which are made up of combinations of gates; so also the input/output relationship of logic systems is summarized in a *Truth Table*. The Truth Table gives a summary in a tabular form of the outputs

which result from the several combinations of the inputs to a logic gate or a combination of logic gates. For analyzing the performance of a logic circuit. it is useful to work out a truth table for the evaluation of output for the different input combinations.

Truth tables for both positive and negative logic for basic logic gates are given in Appendix 6. The implementation of logic gates using NAND and NOR logic has also been given in this Appendix for some logic gates.

#### 1.4. LOGIC POLARITY

We have, earlier on, briefly referred to logic polarity. While mostly positive logic is normally employed in designing logic circuits, there are, however, some instances when negative logic is found more convenient. There are also some systems which use both positive and negative logic. By and large most of the systems use positive logic. This implies that + 5 V means logic 1 level and 0 V represents logic 0 level. In actual practice, however, it is not possible to achieve these voltage levels precisely. Logic circuits are therefore so designed that voltages exceeding 2.5 V are taken to be High (logic 1), and voltages less than 0.8 V are considered to be Low (logic 0).

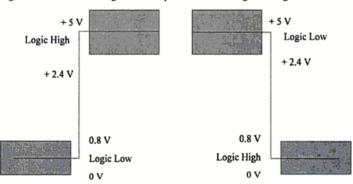

Figure 1.1 shows the voltage level requirements for positive logic and Fig. 1.2 shows the voltage level requirements for negative logic.

Fig. 1.1. Logic levels for positive logic.

Fig. 1.2. Logic levels for negative logic.

#### 1.5. LOGIC TRAINER

The experiments described in this manual can be performed on a Logic Trainer which has the following facilities:

- Regulated Power Supplies

- (a) + 5 V D.C., better than 2%, 1 A.

- (b) + 12 V D.C., better than 1% at 100 mA.

- (c) 12 V D.C., better than 1% at 100 mA.

2. One TTL Compatible Clock: Duty Cycle 45%

Output frequencies: 1 Hz, 1 kHz, 10 kHz and 100 kHz

5 V peak-to-peak, normal and complement outputs.

3. Four Logic Switches

States: Logic High '1' (+5 V)

Logic Low '0' (Ground)

- 4. Four Logic Level Monitors

- Two Bounceless Pushbutton Switches providing complementary pulser outputs of + 5 and + 0.2 V.

For experimenters who are interested in enlarging the scope of these facilities, some circuits have been provided in Appendix 12. The front panel layout of a typical logic trainer is given in Fig. AP-12.1 in Appendix 12. It should help students to follow the instructions given for carrying out experiments.

#### **PROBLEMS**

1.1. State DeMorgan's theorem and use it to simplify the following expressions:

(a)

$$\overline{(A+B)+(C+D)}$$

(b)

$$\overline{\overline{A} \cdot \overline{B}} + \overline{C} + D$$

1.2. Simplify the following Boolean expressions:

(a)

$$B + A \overline{\left(C + \overline{DE}\right)}$$

(b)

$$B + A\overline{B}$$

(c)

$$ABCD + A\overline{B}CD$$

$$(d) \ \overline{1+\overline{B}}$$

(e)

$$\overline{A} + AB + \overline{C} + \overline{B}C$$

$$(f)$$

$\overline{A} + B\overline{C} + A$

1.3. Prove that

$$\overline{A} \cdot \overline{B} = A + B$$

1.4. Prove that

$$\overline{A} + \overline{B} = A \cdot B$$

- 1.5. Illustrate the concept of logic polarity with examples.

- 1.6. From the following examples of logic polarity select those which stand for negative logic polarity:

(a) Logic

$$0 = +.1 \text{ V}$$

Logic  $1 = +3.5 \text{ V}$

- (b) Logic 0 = -6 VLogic 1 = 0 V

- (c) Logic 0 = +15 VLogic 1 = +1 V

- (d) Logic 0 = 0 VLogic 1 = -6 V

- (e) Logic 0 = +1 VLogic 1 = +15 V

- (f) Logic 0 = +3.5 VLogic 1 = +.1 V

# LOGIC FAMILIES

#### 2.1. INTRODUCTION

When we speak of a logic family we are referring to devices which have compatibility within the family in respect of the important parameters like supply voltage, input and output voltage levels, so that within the family different devices may be interconnected. These devices are fabricated using advanced techniques and are called *integrated circuits*. With the help of this technique integrated devices can be made containing a large number of transistors, diodes, resistors etc. They are broadly classified as follows:

| Number of Gates | Integrated Circuit<br>Category | Abbreviation |

|-----------------|--------------------------------|--------------|

| 1-12            | Small Scale Integration        | SSI          |

| 13-99           | Medium Scale Integration       | MSI          |

| 100-9999        | Large Scale Integration        | LSI          |

| 10,000-99,999   | Very Large Scale Integration   | VLSI         |

| Over 100,000    | Ultra High Scale Integration   | UHSI         |

There are two main technologies which are used for the fabrication of integrated circuits. They are the bipolar and CMOS technologies. The most popular family in the bipolar technology is the TTL family. The following families also belong to the bipolar technology:

- Integrated Injection Logic (I<sup>2</sup>L) and

- \* Emitter Coupled Logic

The following families belong to the MOS technology:

- \* CMOS Logic

- \* PMOS Logic and

- NMOS Logic

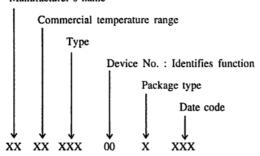

#### 2.2. NUMBERING SYSTEM FOR DIGITAL ICS

Digital ICs carry a number code which is printed on top of the ICs to help in the identification of the devices.

#### The information code is usually as follows:

#### Manufacturer's name

The codes of some of the manufacturers are as follows:

| DM | National Semiconductors |

|----|-------------------------|

| F  | Fairchild               |

| GD | Goldstar                |

| HD | Hitachi                 |

| IM | Intersil                |

| KS | Samsung                 |

| LR | Sharp                   |

| MC | Motorola                |

| MN | Panasonic               |

| N  | Signetics               |

| SN | Texas Instruments       |

| TC | Toshiba                 |

The temperature range for TTL devices is as follows:

7400 series: 0-70°C: It is for commercial applications 5400 series: -55°C to 125°C: For military applications

The type nos. for the TTL ICs are as follows:

| 000   | Standard TTL                    |

|-------|---------------------------------|

| H00   | High Speed TTL                  |

| L00   | Low Power TTL                   |

| S00   | Schottky TTL                    |

| AS00  | Advanced Schottky TTL           |

| LS00  | Low Power Schottky TTL          |

| ALS00 | Advanced Low Power Schottky TTL |

The device nos, for some of the common TTL ICs are as follows:

- 7400 Quad, 2-input NAND gate

- 7402 Ouad, 2-input NOR gate

- 7404 Hex Inverters

- 7408 Quad, 2-input AND gates

- 7410 Triple, 3-input NAND gates

- 7411 Triple, 3-input AND gates

- 7420 Dual, 4-input NAND gates

- 7421 Dual, 4-input AND gates

- 7427 Triple, 3-input NOR gates

- 7430 8-input NAND gate

- 7432 Quad, 2-input OR gates

The codes for package type identification is as follows:

- Plastic DIP (Dual-in-line package) N

- J Ceramic DIP

- D Glass/metal DIP

- w Flat pack

#### 2.3. TTL CHARACTERISTICS

It is important to consider the limitations of these devices in order to get the best possible performance from devices which incorporate them. We will, therefore, consider the parameters which govern their performance.

#### Floating Inputs

If any gate in a TTL package is not used, it is not necessary to make any connections to it. This, however, is not true for CMOS devices. In a CMOS device any unused input must be connected to  $V_{CC}$  or ground.

An open TTL input, that is, one which is not connected is the equivalent of a high input; but it cannot be regarded as a reliable high because noise pulses can drive it low if it is left open. An open input can disable an entire logic system or make its performance erratic.

An unused input should be so connected that the output does not get stuck at any logic level. For instance consider an OR gate. If it has an open input which acquires a logic 1 level, the output will always be logic 1, no matter what you do with the other inputs. In this case the unused input may be connected to other inputs or to ground.

Similarly, if an unused input in an AND gate acquires a logic 0 level its output will get stuck at logic 0 level. The simple rule to be followed is to so connect an unused input to a logic 0 or logic 1 level that the output does not get stuck.

#### Power Dissipation

Specification sheets give the average power dissipation at constant output; but in the active state when the output is constantly changing, power dissipation increases and will exceed 10 mW per gate of a Standard TTL.

#### Propagation Delay Time

The output state of a gate does not change immediately after a change in the input. The time that it takes to change is a measure of the speed at which a logic circuit can operate. Where the speed of operation is important, the propagation delay time has to be maintained within acceptable limits. Because of manufacturing tolerances the propagation delay time may also vary from the nominal indicated values. When a number of gates are cascaded the propagation delay time adds up.

#### Input/Output Logic Levels

Let us consider the valid input and output voltage levels for a TTL device. We will take up the case of an Inverter. According to manufacturer's specifications any input voltage between 0 V to 0.8 V will produce a valid high output voltage. It is listed in data sheets as follows:

$$V_{II} \max = 0.8 \text{ V}.$$

If the low state input voltage exceeds this limit the output will be unpredictable.

Similarly, any voltage from 5.0 V down to 2.0 V can be considered to be a high input voltage for a TTL device. Any voltage within this range will produce a low voltage at the output of an Inverter. The worst case high input voltage is listed in data sheets as follows:

$$V_{IH} \min = 2.0 \text{ V}.$$

If the high state input voltage lies any where between 0.8 V and 2.0 V the output will be unpredictable. According to TTL specification sheets the worst case output voltages are as follows:

> Max low output voltage  $V_{OL}$  max = 0.4 V Min high output voltage  $V_{OH}$  min = 2.4 V

The high state output voltage generally has a value between 2.4 V and 3.9 V. It is typically 3.5 V.

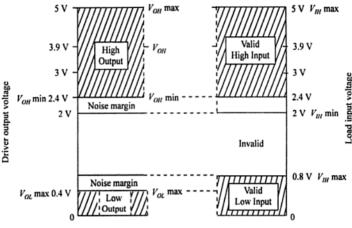

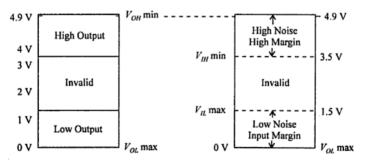

The worst case input and output voltages have been listed below and they have also been indicated on the input and output profiles of TTL devices shown in Fig. 2.1.

Max low output voltage  $V_{OL}$  max = 0.4 V

Min high output voltage  $V_{OH}$  min = 2.4 V

Max low input voltage  $V_{IL}$  max = 0.8 V

Min high input voltage  $V_{\mu\nu}$  min = 2.0 V

In Fig. 2.1 the output voltage range of a TTL driver has been shown alongside the input voltage range of a TTL load. You will notice from this diagram that the output voltage range from 2.4 V to 3.9 V falls within the permissible high input voltage range of 2.0 V to 5.0 V.

From the above discussion you will notice that the low output voltage range 0 V to 0.4 V lies within the low input voltage range 0 to 0.8 V of the TTL load. Also the high output voltage range of 2.4 V to 5 V (normally 3.9 V) lies within the high input voltage range 2 V to 5 V of the TTL load. The driver output voltage is, therefore, fully compatible with the input voltage range of the TTL load.

Fig. 2.1. (a) Output profile of a TTL driver.

Fig. 2.1. (b) Input profile of a TTL load.

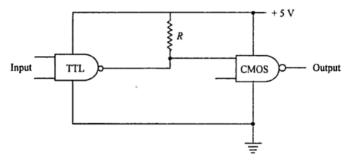

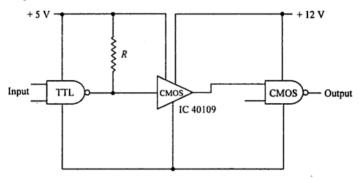

The output of any TTL gate can be connected to the input of any TTL gate. However, it cannot be connected directly to the input of a CMOS gate. This can, however, be done with the help of interfacing devices.

#### Noise Margin

In the presence of a noise voltage not exceeding 0.4~V the minimum high level driver output will change to 2.4-0.4~V or 2~V in the negative direction and 2.4+0.4~v or 2.8~V in the positive direction. These voltage levels are within the acceptable limits and this noise voltage will not cause any problem as long as the noise voltage is within 0.4~V. The noise margins have been shown in Fig. 2.1. However, if the noise voltage exceeds this figure it will lead to triggering of the TTL load.

### Sourcing and Sinking of Current

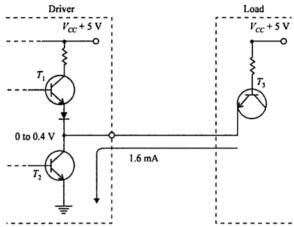

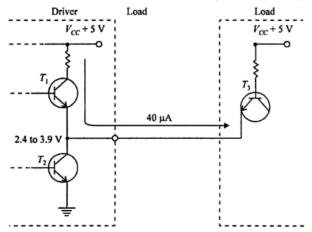

When the TTL driver is connected to a load and the driver's output is low, current flows from the load to the driver. From a unit load (single emitter) the maximum current will not exceed 1.6 mA. The driver transistor is said to sink a current of 1.6 mA.

When the driver output is high a current of 40  $\mu A$  flows from the driver to the load. The driver now acts as a current source. Figure 2.2 shows the magnitude and direction of the current.

A standard TTL device is capable of sinking a current of 16 mA when its output is low and can source a current of upto 400  $\mu$ A when its output is high.

Fig. 2.2. (a) shows direction and magnitude of current flowing from TTL load to TTL driver when the driver output is low (0-0.4 V).

Fig. 2.2. (b) shows direction and magnitude of current flowing from TTL driver to TTL load when the driver output is high (2.4-3.9 V).

#### Fan-in and Fan-out

Since a TTL driver can sink up to 16 mA of current when its output is low and a unit TTL load needs to sink only 1.6 mA of current; 10 emitters

(unit loads) can be connected to the output of a TTL driver. It means that the Fan-out is ten. Also when the driver output is high it can source a current of 400  $\mu$ A and since a TTL load requires a source current of only 40  $\mu$ A, it can source 10 emitters (unit loads).

When a TTL load has 2 emitters (2 unit loads), only five loads of this type can be connected to the driver. We say that the Fan-in of this load is two.

#### Power Supply

TTL devices require a power supply of 5 volts  $\pm$  5%. Since TTL devices are susceptible to ripple, the power supply should have good regulation. As a further precaution a 0.01 to 0.1  $\mu$ F capacitor should be connected from +  $V_{CC}$  to ground for each group of 4 or 5 TTL integrated circuits. For the supply voltage requirements of TTL sub-families data sheets should be consulted.

#### 2.4. TTL SUB-FAMILIES

As designers' requirements in respect of power consumption, propagation delay, noise margin, fan-out etc. are not quite met by the standard TTL series, many sub-families, listed below, have been developed to meet these requirements:

| 74H   | High Speed                  |

|-------|-----------------------------|

| 74L   | Low Power                   |

| 748 . | Schottky                    |

| 74LS  | Low Power Schottky          |

| 74AS  | Advanced Schottky           |

| 74ALS | Advanced Low Power Schottky |

We will consider some of the special features of these sub-families.

#### 74H Series

Although they are faster than standard TTL; but they consume a lot of power as they use resistors of lower values. This series is, therefore, nearly obsolete.

#### 74L Series

This series is useful where very low power consumption is essential; but it is also much slower than standard TTL.

#### 74S Series

Known as the Schottky TTL series, it is much faster than the standard TTL.

#### 74LS Series

Offers a good compromise between speed and power dissipation. Power consumption is about one-fifth of the standard TTL series and the low power Schottky series. This series is, therefore, used more than other series in the TTL range.

#### 74AS Series

This series is of special value where speed is a critical requirement and power consumption is not so important.

#### 74ALS Series

These devices are the most advanced in the TTL family. Power dissipation per gate is only 1 mW and propagation delay is only 4 ns.

#### Summary of TTL Family Specifications

Parameters specified by manufacturers to define the operating characteristics of ICs are given in Table 2.1. Characteristics of TTL, IC families which we have discussed so far are given in Table 2.2.

Table 2.1

| Glossary of Symbols used to | Specify | the |

|-----------------------------|---------|-----|

| Operating Characteristics   | of ICs  |     |

| <br>0 1 111                 |         |     |

- $V_{cc}$ Supply Voltage

- $V_{1H}$ High Level Input Voltage: This is the minimum input voltage which is recognized as logic '1' by the gate.

- Low Level Input Voltage: This is the maximum input voltage which  $V_{1L}$ is recognized as logic '0' by a gate.

- High Level Output Voltage: This is the minimum voltage at the  $V_{\alpha\mu}$ output corresponding to logic '1'.

- Low Level Output Voltage: This is the maximum voltage at the  $V_{0L}$ output which will correspond to logic '0'.

- Supply Current: The current into the  $V_{CC}$  supply terminal of an IC.  $I_{cc}$

- High Level Supply Current: This is the supply current when the  $I_{1CCH}$ output of the gate is at logic '1'.

- Low Level Supply Current: This is the supply current when the  $I_{CCL}$ output of the gate is at logic '0'.

- High Level Input Current: This is the current into the input when a  $I_{1H}$ high level voltage is applied to that input.

- Low Level Input Current: This is the current into an input when a  $I_{1L}$ low level voltage is applied to that input.

- High Level Output Current: This is the maximum current which the  $I_{0H}$ gate can source in logic '1' level at the output.

- $I_{0L}$ Low Level Output Current: This is the maximum current which the gate can sink in logic '0' level at the output.

- Propagation Delay Time: High to Low Level Output: This is the t<sub>PHL</sub> delay time when the output goes from high to low level at the output.

- Propagation Delay Time: Low to High Level Output: This is the  $t_{\rm PLH}$ delay time when the output goes from low to high level at the output.

- Propagation Delay Time: This is the time between reference points on  $t_{\rm pd}$ the input and output voltage waveforms with the output changing from one level (high or low) to the other level  $(t_{pd} = t_{pHL})$  or  $t_{pLH}$ .

|                                 |       |       | and acteris | characteristics of LLL ic Family | C ramily   |                    |        |             |

|---------------------------------|-------|-------|-------------|----------------------------------|------------|--------------------|--------|-------------|

|                                 |       |       |             | TTL F                            | TTL FAMILY |                    |        |             |

| PARAMETER                       | 7400  | 5400  | 74H00       | 54L00                            | 74S00      | 74AS00             | 74LS00 | 74ALS00     |

| V <sub>CC</sub> (V) Min         | 4.75  | 4.5   | 4.75        | 4.5                              | 4.75       | 4.5                | 4.75   | 4.5         |

| V <sub>cc</sub> (V) Max         | 5.25  | 5.5   | 5.25        | 5,5                              | 5.25       | 5.5                | 5.25   | 5.5         |

| V <sub>III</sub> (V) Min        | . 2.0 | 2.0   | 2.0         | 2.0                              | 2.0        | 2.0                | 2.0    | 2.0         |

| V <sub>R.</sub> (V) Max         | 8.0   | 8.0   | 8.0         | 0.7                              | 8.0        | 8.0                | 8.0    | 8.0         |

| V <sub>OH</sub> (V) Min         | 2.4   | 2.4   | 2.4         | 2.4                              | 2.7        | V <sub>cc</sub> -2 | 2.7    | $V_{cc}$ -2 |

| V <sub>oL</sub> (V) Max         | 0.4   | 0.4   | 0.4         | 0.3                              | 0.5        | 0.5                | 5.0    | 0.4         |

| $I_{IL}$ (mA) Max               | -1.6  | -1.6  | - 2.0       | - 0.18                           | - 2.0      | - 0.5              | - 0.4  | - 0.1       |

| <i>I</i> <sub>IH</sub> (mA) Мах | 0.04  | 0.04  | 0.05        | 0.01                             | 0.05       | 0.02               | 0.02   | 0.02        |

| <i>I<sub>ot.</sub></i> (mA) Мах | 16    | 16    | 20          | 2                                | 20         | 20                 | 80     | œ           |

| I <sub>OH</sub> (mA) Max        | - 0.4 | - 0.4 | - 0.5       | - 0.1                            | - 1.0      | - 2.0              | - 0.4  | - 0.4       |

| r <sub>phi</sub> (ns)           | 7     | 7     | 9           | 31                               | 5          | 4                  | 10     | ∞           |

| ι <sub>ρύλ</sub> (ns)           | 11    | 11    | 9           | 35                               | 5          | 4.5                | 6      | =           |

| P <sub>d</sub> (per gate) mW    | 01    | 10    | 22          | -                                | 61         | 80                 | 2      | 1.2         |

|                                 |       |       |             |                                  |            |                    |        |             |

#### 2.5. MOS FAMILY CHARACTERISTICS

In the MOS family the P-channel devices have almost gone out of use and the N-channel devices are used mostly in large scale ICs. This leaves the CMOS family which uses both N-channel and P-channel MOSFETS. We will, therefore, confine our discussion to the characteristics of the CMOS devices.

#### Power Supply

CMOS devices can work over a voltage range extending from about 3 to 15 V. The disadvantage with a high supply voltage is that dissipation increases and it may even cause excessive heating. However, the advantage with a high operating voltage is decreased susceptibility to noise pick up. Operation at much lower voltages is accompanied by some adverse effects. It increases propagation delay and decreases noise immunity. In circumstances where the determining factors are propagation delay and noise immunity, the operating voltage should preferably be higher than 9 V.

#### Power Dissipation

The static power dissipation of a CMOS gate is about 10 nW. However. CMOS gates consume more power during a change of state, from high to low or low to high. Power dissipation also depends on the switching speed and at 1 MHz the dissipation increases to 1 mW.

#### Floating Inputs

With a floating input, as it is capacitative, and the input has very high impedance, the time constant may be very high, resulting in erratic and unpredictable behaviour. If the input capacitance acquires sufficient charge, it may even bias the input transistor to operate in the linear operating region. which will totally upset the system operation and the current consumption may become excessive. CMOS inputs should not, therefore, be left floating. Methods suggested earlier may be adopted.

#### Sourcing and Sinking of Current

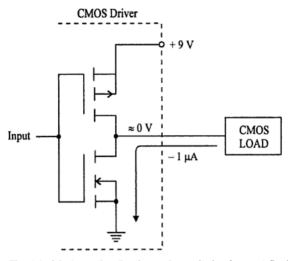

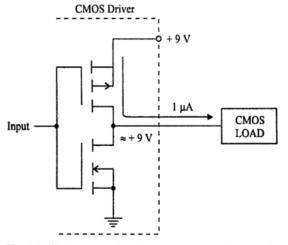

In CMOS devices the currents are very much smaller than in TTL devices. Figure 2.3 (a) shows that when the driver output is low the driver can sink a current of 1 uA. Figure 2.3 (b) shows that when the driver output is high it can source a current of 1µA. In the first case the current has a negative sign as the current is flowing out of the load when the driver output is low.

$$I_{OL} \max = -1 \mu A$$

In the second case the current has a positive sign as it is flowing into the load

$$I_{OH}$$

max = 1  $\mu$ A

Fig. 2.3. (a) shows the direction and magnitude of current flowing from a CMOS load to a CMOS driver when the driver output is low (≈ 0 V).

Fig. 2.3. (b) shows the direction and magnitude of current flowing from a CMOS driver to a CMOS load when the driver output is high (≈ + 9 V).

#### Input/Output Logic Levels

The input/output logic levels for voltages and currents for CMOS IC families are given in Table 2.3. We are reproducing below the input/output voltage levels for CMOS devices in the 4000A and 4000B series when operated from a 5 V supply.

The worst case voltages are as follows:

$$V_{IH}$$

min 3.5 V

$V_{IL}$  max 1.5 V

$V_{OH}$  min 4.9 V

$V_{OL}$  max 0.01 V

The input/output profiles for these CMOS sub-family are shown in Fig. 2.4. You will observe that the input and output logic levels for the CMOS driver of the 4000A/B series fall within the acceptable high and low input voltage levels of the CMOS load. There is, therefore, no interfacing problem between the driver and the load and they can be directly connected. However, there may be interfacing problem between a CMOS driver and a TTL load or vice-versa. This problem will be discussed later in one of the chapters.

Fig. 2.4. (a) showing the output profile and noise margins for a CMOS driver.

Fig. 2.4. (b) showing the input profile for a CMOS load.

#### 2.6. CMOS SUB-FAMILIES

The 4000A series was the first sub-family in the CMOS category; but it was not very popular as it had very little output drive. This led manufacturers to introduce the 4000B series which had the same functions as the 4000A series and was in many ways similar to it. The main problem of compatibility with TTL devices remained unsolved.

These problems led to the introduction of the 54C/74C series of CMOS devices. This new series performs the same functions and has the same pin connections as the 54/74 TTL family. The 54C series has a temperature range of - 55°C to + 125°C. For the 74C series the temperature range is - 40°C to + 85°C. Both these sub-families have a supply voltage range of 3 to 15 V. The specifications for 74C sub-family are given in Table 2.3. Quite a large variety of CMOS ICs in the 74C sub-family are available. A list of the currently available ICs in this category is given in Appendix 8.

A high speed series of CMOS devices, 74HC is also now available. They have the same logic functions and pin numbers as the corresponding TTL devices. The 74HC series has a shorter propagation delay than the 74C series. The output low  $(I_{OL})$  and output high  $(I_{OH})$  current of 4 mA in 74HC devices is sufficient to drive more than one TTL device directly.

74HCT is another sub-family in the CMOS category. This sub-family has better compatibility with TTL devices than the 74HC series. If you refer to Table 2.3 you will observe that all the CMOS sub-families which we have discussed can be operated from a power supply of + 5 V.

#### Propagation Delay Time

The propagation delay time of CMOS devices has quite a large range and it is much more than for TTL devices. Cascading of CMOS devices further aggravates the problem.

#### Noise Margin

CMOS devices have a noise margin of 45% of  $V_{CC}$  which is considerably better than for TTL devices. With an operating voltage of 12 V, the noise margin will be 5.4 V. This implies that the connecting link between the driver and the load will not be susceptible to noise interference unless the peak value of the noise exceeds 5.4 V. Figure 2.4 (b) shows the noise margins when the operating voltage is 5 V.

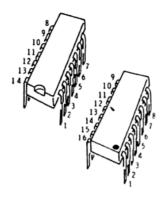

#### 2.7. INTEGRATED CIRCUIT PACKAGING

There are many types of packages for ICs; but conventional logic gates are often supplied in 14-pin or 16-pin DIL (Dual-in-line) packages. Figure 2.5 shows a 14-pin and a 16-pin DIL package. It should be noted that the diagrams show the devices as viewed from the top, not from the underside. In both the cases the IC pins are numbered sequentially, starting from the notch (or dot) and moving in the anti-clockwise direction.

Fig. 2.5. showing 14-pin and 16-pin DIL package pin numbering as viewed from the top of the package.

Table 2.3 Characteristics of CMOS IC Families

| PARAMETER                | 4000A | 4000B        | 74C00  | 74HC00 | 74HCT00 |

|--------------------------|-------|--------------|--------|--------|---------|

| V <sub>CC</sub> (V) Min  | 3     | 3            | 3      | 2      | 4.5     |

| V <sub>CC</sub> (V) Max  | 15    | 18           | 15     | 6      | 5.5     |

| Oper. @ (V)              | 5     | 5            | 5      | 4.5    | 4.5     |

| V <sub>IH</sub> (V) Min  | 3.5   | 3.5          | 3.5    | 3.15   | 2       |

| V <sub>IL</sub> (V) Max  | 1.5   | 1.5          | 1.5    | 0.9    | 0.8     |

| V <sub>OH</sub> (V) Min  | 4.5   | 4.5          | 4.5    | 4.4    | 4       |

| V <sub>OL</sub> (V) Max  | 0.01  | ± 0.01       | 0.5    | 0.1    | 0.33    |

| I <sub>IL</sub> (μA) Max | 10 pA | ± l          | 1      | - 1    | 0.1     |

| I <sub>II</sub> (μA) Max | 10 pA | 1            | - 1    | 1      | 1       |

| I <sub>OL</sub> (mA) Min | 0.12  | 0.4          | 1.75   | 4      | 4       |

| I <sub>OH</sub> (mA) Min | 0.12  | 1.6          | - 1.75 | 4      | 4       |

| t <sub>PHL</sub> (ns)    | 180   | 160 -<br>320 | 90     | 23     | 20      |

| t <sub>PLH</sub> (ns)    | 125   | 210 -<br>420 | 90     | 23     | 20      |

Note: Specifications for 74C, 74HC and 74HCT families are for specific devices.

#### PROBLEMS

- 2.1. Define the following parameters:

- (a)  $V_{OL}$  Max (b)  $V_{OH}$  (c)  $V_{IH}$  Min (d)  $I_{IH}$ .

- 2.2. For the TTL 7400 series what are the  $V_{I\!H}$  Min and  $V_{I\!L}$  Max voltages ?

- 2.3. Why does the output current corresponding to logic '0' level of a TTL IC have a negative sign, and why does the output current corresponding to logic '1' level have a positive sign?

- 2.4. Refer to the specifications of TTL IC 7400 and calculate its fan-out.

- 2.5. Explain the disadvantages of a floating gate.

- 2.6. Only two inputs of an AND gate having three inputs have been used. What happens if it is left floating?

- 2.7. In the above problem how will you handle the third input to avoid problems?

- 2.8. In an OR gate having three inputs only two inputs are being used. Will you connect the third input to ground or to  $V_{CC}$ ?

- 2.9. What is an acceptable low level input voltage for a TTL IC ? What happens if it is more or less than  $V_{II}$  ?

- 2.10. If the minimum high input voltage to a TTL gate is less than  $V_{IH}$  min what effect will it have on its performance?

- 2.11. What is the highest valid low input voltage for a TTL gate ?

# **INVERTERS: BUFFERS**

#### 3.1. INTRODUCTION

In this chapter we will study the functioning and characteristics of Inverters and Buffers. Both these electronic devices have a single input and a single output. However, there is a basic difference in their functioning. Whereas Inverters complement any input applied to them; the Buffers allow the input signal to pass through without any change. Inverters are used to complement a signal and the Buffers are used to isolate the input from the output.

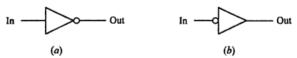

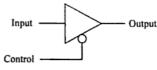

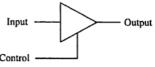

The symbols for an Inverter are shown in Fig. 3.1 (a) and Fig. 3.1 (b). Both these symbols are in use. The triangle in these symbols indicates an amplifier and the bubbles signify inversion or complementation. The basic function of an Inverter is given in Truth Table 3.1.

Fig. 3.1. Inverter symbols.

# Table 3.1 Inverter Truth Table

| Input | Output         |

|-------|----------------|

| Α     | $\overline{A}$ |

| 1     | 0              |

| 0     | 1              |

The following are some of the important points to be remembered about an Inverter:

- A LOW input produces a HIGH output and a HIGH input produces a LOW output.

- \* For an Inverter, the output is always the opposite of the input. If the input is logic 0, the output is logic 1 and if the input is logic 1, the output is logic 0.

\* In other words, the output is always the complement of the input. The Inverter is sometimes called a NOT gate as the output is opposite of the input.

#### Buffer

The symbol for a Buffer is given in Fig. 3.2. If the input to a Buffer is A, the output is also A. If two Inverters are connected in cascade, the circuit behaves like a non-inverting amplifier. In other words, for a logic 1 input the output is also logic 1 and for a logic 0 input the output is also logic 0. During the course of the following experiment you will observe that an even number of Inverters in tandem act as a non-inverter (buffer) and an odd number in tandem invert the input signal.

Fig. 3.2. Buffer symbol.

A Buffer is used as a non-inverting amplifier to isolate two other devices. Buffers have a high input and a low output impedance. This means a low input current and a high output current. A basic gate does not provide adequate isolation of two devices as the input current of a TTL gate is only about one-tenth of the output current. IC 7437 is a quad 2-input NAND Buffer in which the output current can be as much as thirty times the input current.

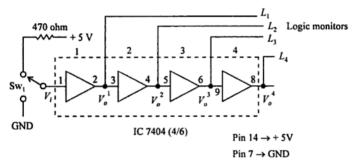

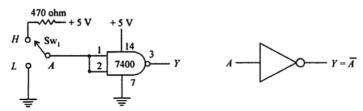

#### **EXPERIMENT 3.1: INVERTERS**

#### Objective

To study the operation and characteristics of Inverters.

#### Materials Required

Logic trainer

Volt-ohm-milliammeter (VOM)

TTL Hex Inverter IC 7404

Resistor 470 ohm

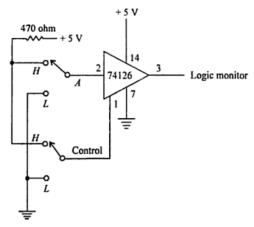

#### Procedure

- Connect the circuit shown in Fig. 3.3. The Hex Inverter used in this

experiment contains six identical and independent Inverters, only four

of which are used in this experiment.

- The input for the Inverter is obtained through logic switch Sw<sub>1</sub>, which

can connect the input either to +5 V for a high logic input or to

ground for a low input.

- The output of each of the Inverters is connected to Logic monitors (LEDs). The LEDs light up on a high Inverter output and are off when the Inverter output is low.

- 4. Connect pin 14 of the IC to  $V_{CC}$  (+ 5 V dc) and pin 7 to ground (Gnd).

- You will measure the input and output voltage of Inverters with a Voltmeter and also observe the output on the Logic monitors.

- Now measure the input (V<sub>i</sub>) and output (V<sub>o</sub>) voltages with both low and high input positions and logic switch Sw<sub>1</sub>. You will record the input voltage and the output of each of the Inverters and enter your observations in Table 3.2.

Fig. 3.3

Table 3.2

|   | Input V <sub>i</sub><br>Volt | Output V <sub>o</sub> <sup>1</sup><br>Volt | Output V <sub>o</sub> <sup>2</sup><br>Volt | Output V <sub>o</sub> <sup>3</sup> Volt | Output V <sub>o</sub> <sup>4</sup><br>Volt |

|---|------------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------|--------------------------------------------|

| 1 |                              |                                            |                                            |                                         |                                            |

| 2 |                              |                                            |                                            |                                         |                                            |

Now using positive logic assignments convert the voltage levels in Table 3.2 into logic 1s and 0s and write your result in Table 3.3.

Table 3.3

|   | $V_{i}$ | $V_o^{-1}$ | $V_o^2$ | $V_o^3$ | V <sub>o</sub> <sup>4</sup> |

|---|---------|------------|---------|---------|-----------------------------|

| 1 |         |            |         |         |                             |

| 2 |         |            |         |         |                             |

#### Discussion of Data

- You applied logic 0 and logic 1 data at the input of Inverter 1 and measured the resultant outputs of Inverters 1, 2, 3 and 4.

- 2. Your observations as recorded in Table 3.2 showed that when input, V<sub>i</sub>, to Inverter 1 was logic 0 or 1 the outputs of Inverters 1 and 3 showed complementation of the input V<sub>i</sub>. This leads to the conclusion that an odd number of Inverters in tandem complement the input.

- 3. Your observation also showed that when input to Inverter 1 was 0 or 1, the outputs of Inverters 2 and 4 was the same as the input to Inverter 1. This meant that an even number of Inverters act as a Buffer and do not complement the input.

#### PROBLEMS

- 3.1. If you have to use Inverters as Buffers, will you use two Inverters, four Inverters or an even larger number?

- 3.2. In the above example, do you see any problem in using a large number of Inverters?

- 3.3. List as many applications of Inverters as you can think of.

# AND : OR GATES

#### 4.1. INTRODUCTION

Logic circuits are basically of two types: decision-making circuits and memory circuits. Their functioning depends on the binary inputs they receive and produce binary outputs which are a function of the inputs as well as of the characteristics of the logic circuit they employ.

After you have become familiar with the basic logic elements, common configurations of these devices and their characteristics, you will be in a position to evaluate the operation of digital equipments in common use and also acquire capability for designing digital devices.

Logic gates are the basic decision-making elements. Logic gates have a single output and they may have two or more inputs. For specific decision-making functions there are several types of gates. Gates are supplied binary inputs and produce an output, which is a function of their characteristics and the nature of the inputs. The output shows the decision made by gates. In this chapter, we will discuss the operation and characteristics of AND and OR gates.

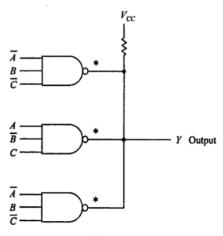

#### 4.2. AND GATES

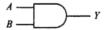

The AND gate has two or more inputs and a single output. The logic symbol for an AND gate is given in Fig. 4.1.

Fig. 4.1. Logic symbol for 2-input AND gate.

The distinctive characteristics for an AND gate are as follows :

- \* The output of the AND gate is logic 1 only if all the inputs are logic 1.

- \* If any one or more inputs are logic 0, the output will be logic 0.

The first characteristic of the AND gate cited above makes it an ideal control element. A single input will control the output irrespective of the state of the other input. The truth table for a 2-input AND gate is given in Table 4.1. The truth table indicates how it will perform under the different conditions of the states of the inputs A and B. Since there are two inputs, the total number of input combinations will be  $2^2$  or 4.

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | Y      |

| 0   | 0    | 0      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1 1  | 1      |

Table 4.1 Truth Table for a 2-input AND Gate

You will notice from the truth table that the output is logic 0 when either of the two or both inputs are logic 0. The output is logic 1 only when both the inputs are logic 1.

The logical operation performed by the AND gate is expressed as follows in Boolean algebra.

$$Y = A \cdot B = AB$$

The AND function is designated by the dot (·) between the input variables A and B. It is read as Y equals A AND B.

The 2-input AND gate can be compared to a switching circuit shown in Fig. 4.2. This circuit will produce a high output which will light up the lamp only when both the switches are closed. When any one or both the switches are open the lamp will not light up. This circuit will have the same truth table as the one shown in Table 4.1 for a 2-input AND gate.

Fig. 4.2. 2-variable switching circuit.

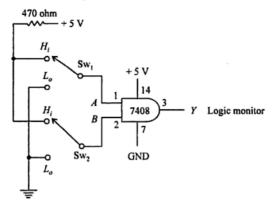

# EXPERIMENT 4.1: TWO-INPUT AND GATE

# Objective

To verify the operation and characteristics of the two-input AND gate.

# Materials Required

Logic trainer

Volt-ohm-milliammeter (VOM)

TTL IC 7408 : Quad 2-input AND gates

Resistor 470 ohm

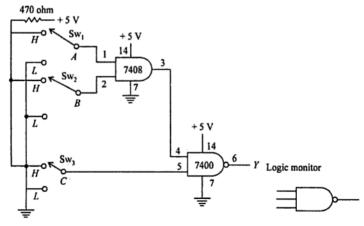

The circuit for the experiment is given in Fig. 4.3.

Fig. 4.3. Circuit for AND gate Experiment 4.1.

- Connect the circuit shown in Fig. 4.3. The IC used in this experiment contains four identical and independent AND gates only one of which has been used in this experiment.

- The input for the AND gate is obtained through logic switches Sw<sub>1</sub> and Sw<sub>2</sub> which can connect the input either to +5 V for a high logic input or to ground for a low logic input.

- The output of the AND gate is connected to a Logic monitor (LED) which lights up on a high output and is off when the output is low.

- 4. Connect pin 14 of the IC to  $V_{CC}$  (+ 5 V) and pin 7 to ground (GND).

- Now, with all possible combinations of Sw<sub>1</sub> and Sw<sub>2</sub> (high and low input states), record the output voltage in truth table [Table 4.2 and also observe the state of the Logic monitor (LED)].

Table 4.2

Truth Table for a 2-input AND Gate

|   | Inputs |       | Output |

|---|--------|-------|--------|

|   | Α      | В     | Y      |

| 1 | 0 V    | 0 V   |        |

| 2 | 0 V    | + 5 V |        |

| 3 | + 5 V  | 0 V   |        |

| 4 | + 5 V  | + 5 V |        |

Now using positive logic assignments convert the voltage levels in Table 4.2 into logic 1s and 0s and enter your result in Table 4.3.

Table 4.3

Truth Table for 2-input AND Gate with Positive Logic Assignments

| . [ | Inputs |   | Output |

|-----|--------|---|--------|

|     | Α      | В | Y      |

| 1   |        |   |        |

| 2   |        |   |        |

| 3   |        |   |        |

| 4   |        |   |        |

Your readings in Table 4.3 should tally with the truth table for a positive logic 2-input AND gate in Appendix 6.

Now using negative logic assignments convert the voltage levels in Table 4.2 into logic 1s and 0s and enter your result in Table 4.4

Table 4.4

Truth Table for 2-input AND Gate with Negative Logic Assignments

|   | Inputs |   | Output |

|---|--------|---|--------|

|   | Α      | В | Y      |

| 1 |        |   |        |

| 2 |        |   |        |

| 3 |        |   |        |

| 4 |        |   |        |

Your observations in Table 4.4 should tally with the truth table for negative logic of a 2-input AND gate as given in Appendix 6. If you look at the truth table for a 2-input OR gate at S. No. 7, column 4 of Appendix 6 using positive logic you will find that the two tables are identical. This shows that an AND gate using negative logic functions as an OR gate with positive logic. This shows the dual nature of logic gates.

The symbol for an AND gate using negative logic is given in Fig. 4.4.

Fig. 4.4. Symbol for AND gate using negative logic. (Functions as positive OR)

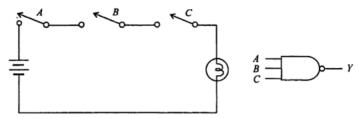

#### Three-input AND Gate

The mechanical equivalent of a 3-input AND gate is like a circuit with three switches wired in series as shown in Fig. 4.5 (a) and its electronic symbol is given in Fig. 4.5 (b). In this arrangement the bulb will light up when all the switches are switched on. If a single switch is off the bulb will not light up. This feature is reflected in the truth table for the 3-input AND gate in Table 4.5.

Fig. 4.5 (a) Mechanical equivalent of a 3-input AND gate.

Fig. 4.5 (b) Symbol for 3-input AND gate.

|   | Inputs | Output |   |

|---|--------|--------|---|

| A | В      | С      | Υ |

| 0 | 0      | 0      | 0 |

| 0 | 0      | 1      | 0 |

| 0 | 1      | 0      | 0 |

| 0 | 1      | 1      | 0 |

| 1 | 0      | 0      | 0 |

| 1 | 0      | 1      | 0 |

| 1 | 1      | 0      | 0 |

Table 4.5 Truth Table for a 3-input AND Gate

A 3-input AND gate will have 23 or 8 states. In the truth table these 8 states are shown by the binary equivalents of the 8 states (0 through 7 in decimal form).

You will notice from the truth table that the output is high only when all the inputs are high and the output is low when any one or more inputs are low.

The operation of a 3-input AND gate can be stated as follows in algebraic form.

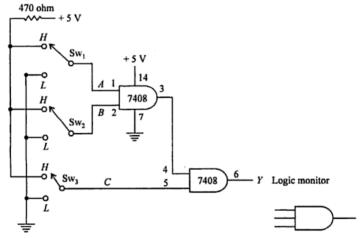

### **EXPERIMENT 4.2: THREE-INPUT AND GATE**

#### Objective

- \* To build a 3-input AND gate using two 2-input AND gates.

- \* Draw up truth tables using positive and negative logic.

# Materials Required

Logic trainer

Volt-ohm-milliammeter (VOM)

TTL IC 7408: Quad 2-input AND gates

Resistor 470 ohm

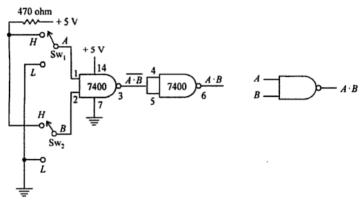

The circuit for the experiment is given in Fig. 4.6.

Fig. 4.6. 3-input AND gate assembled using 2-input AND gates.

Fig. 4.7. Symbol for 3-input AND gate.

- Connect the circuit shown in Fig. 4.6. Only two AND gates from the IC have been used.

- The AND gate inputs can be connected through switches to high (H) and low (L) inputs.

- 3. The output of the lower AND gate is connected to the Logic monitor.

- 4. Connect pin 14 of the IC to  $V_{CC}$  (+5 V) and pin 7 to ground.

- 5. Now connect switches Sw<sub>1</sub>, Sw<sub>2</sub> and Sw<sub>3</sub> to the logic levels shown in the eight sets of inputs in Truth Table 4.5 and record the result of each input combination in Table 4.6 and compare this table with Table 4.5. Since both the tables use positive logic assignment, they should be identical.

Table 4.6

Truth Table for 3-input AND Gate with Positive Logic Assignment

|   | Inputs | <b>.</b> | Output |

|---|--------|----------|--------|

| A | В      | С        | Y      |

| 0 | 0      | 0        |        |

| 0 | 0      | i        |        |

| 0 | 1      | 0        |        |

| 0 | 1      | 1        |        |

| 1 | 0      | 0        |        |

| 1 | 0      | 1        |        |

| 1 | 1      | 0        |        |

| 1 | 1      | 1        |        |

Table 4.7

Truth Table for 3-input AND Gate with Negative Logic Assignment

| regulate Logic Floorighment |   |        |   |

|-----------------------------|---|--------|---|

| Inputs                      |   | Output |   |

| A                           | В | С      | Y |

|                             |   |        |   |

|                             |   |        |   |

|                             |   |        |   |

| ŀ                           |   |        |   |

|                             |   |        |   |

|                             |   |        |   |

| - 1                         |   |        |   |

- 6. Now draw up a truth table for the 3-input NAND gate using negative logic assignment. To do this substitute 1s for 0s and 0s for 1s in Table 4.6 and enter the result in Table 4.7. From this truth table you can draw the following conclusions:

- \* The output is 0 only when all the inputs are also 0.

- \* The output is 1 when at least one of the inputs is 1.

When you come to the subject of OR gates you will observe that these two properties are the characteristic features of an OR gate with positive logic assignment. You can, therefore, conclude that a 3-input AND gate with negative logic assignment functions as an OR gate with positive logic assignment.

The logic symbol for this 3-input AND gate with negative logic assignment is as given in Fig. 4.8.

Fig. 4.8. Symbol for 3-input AND gate using negative logic assignment. (Functions as positive OR)

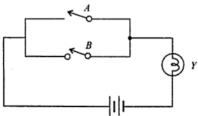

#### 4.3. OR GATES

The OR gate has two or more inputs and a single output as shown in Fig. 4.9.

Fig. 4.9. Logic symbol for 2-input OR gate.

The distinctive characteristics for an OR gate are as follows:

- \* The output of an OR gate is logic 0 only when all inputs are logic 0.

- \* The output of an OR gate is logic 1 when any one or more inputs are logic 1.

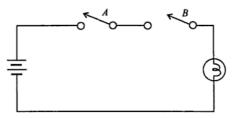

The mechanical equivalent of a 2-input OR gate is like a circuit with two switches connected in parallel as shown in Fig. 4.10. In this arrangement the bulb will light up when any one or both the switches are turned on. If both the switches are off the bulb will not light up. This feature is reflected in the truth table, Table 4.8. As the circuit has two switches there will be  $2^2$  or 4 input combinations for the switches. The truth table, therefore, shows four input combinations.

Fig. 4.10. Mechanical equivalent of a 2-input OR gate.

Table 4.8

Truth Table for a 2-input OR Gate

| Inputs |   | Output |

|--------|---|--------|

| A      | В | Y      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| i      | 0 | 1      |

| 1      | 1 | 1      |

You will notice from this truth table that the output is 0 when both the inputs are 0. You will notice that in the remaining three cases at least one of the inputs is 1 and in these cases the output is also 1. The output of the OR gate is a function of both the inputs A and B. In equation form it is written as follows:

$$Y = A + B$$

The plus sign is an indication, in logic terms, that the logical sum operation (called disjunction of terms so connected) has taken place. The terms so connected are said to be ORed. The symbol + is not the same as the algebraic symbol for addition.

We have considered a 2-input OR gate; but like the AND gate the OR gate may also have more than two inputs. Truth Table 4.9 shows the truth table for a 3-input OR gate.

|   | Inputs | u o mput o | Output |

|---|--------|------------|--------|

| A | В      | С          | Y      |

| 0 | 0      | 0          | 0      |

| 0 | 0      | 1          | 1      |

| 0 | 1      | 0          | 1      |

| 0 | 1      | 1          | 1      |

| 1 | 0      | 0          | 1      |

| 1 | 0      | 1          | 1      |

| 1 | 1      | 0          | 1      |

| 1 | 1      | 1          | 1      |

Table 4.9 Truth Table for a 3-input OR Gate

You will notice from this truth table that the output is 0 only in one case and that is when all inputs are 0. In the remaining cases the output is 1 since at least one of the inputs is 1.

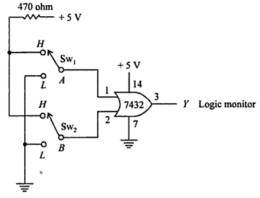

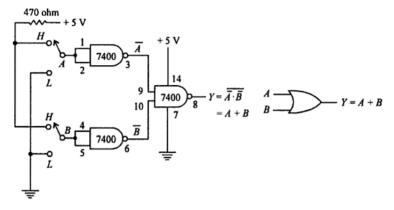

# EXPERIMENT 4.3: TWO-INPUT OR GATE

# Objective

To draw up truth tables for a 2-input OR gate using positive and negative logic.

# Materials Required

Logic trainer

Volt-ohm-milliammeter (VOM)

TTL IC 7432: Quad 2-input OR gates

Resistor 470 ohm

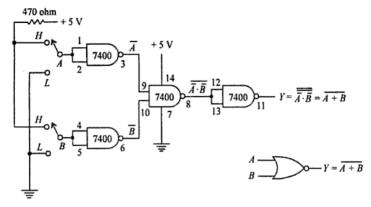

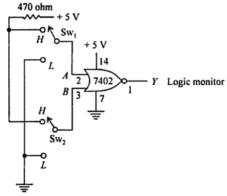

The circuit for the OR gate Experiment 4.3 is given in Fig. 4.11.

Fig. 4.11. Circuit for OR gate Experiment 4.3.

- Connect the circuit given in Fig. 4.11. Only two OR gates from the IC have been used.

- 2. Now connect pin 14 of IC to +5 V and pin 7 to ground.

- Follow the input combinations of Table 4.8 and set switches Sw<sub>1</sub> and Sw<sub>2</sub> to each combination of the inputs.

- Observe the output as shown by the logic monitor and record the result for each input combination in Table 4.10.

- As your experiment was intended for positive logic assignment your observations should tally with Table 4.8 which was also for positive logic assignment.

Table 4.10

Truth Table for 2-input OR Gate using Positive Logic Assignment

| Inp | outs | Output |

|-----|------|--------|

| A   | В    | Y      |

|     |      |        |

|     |      |        |

|     |      |        |

|     |      |        |

|     |      |        |