al Pages: 3

## 2022

## 3rd Semester Examination PHYSICS (Honours)

Paper: C7-T

## [Digital Systems and Applications]

[CBCS]

Full Marks: 40

Time: Two Hours

The figures in the margin indicate full marks. Candidates are required to give their answers in their own words as far as practicable.

Answer any *five* of the following:  $2 \times 5 = 10$

- 1. Add  $(-12)_{10}$  and  $(-14)_{10}$  using the 1s complement method.

- 2. Find the value of base r if  $(121)_r = (144)_8$ .

- 3. Subtract hexadecimal number  $(C5A)_{16}$  from  $(B3D)_{16}$  using 15s complement method.

- 4. Show that  $B\overline{C} + AB + AC = AC + B\overline{C}$ .

- 5. Write down the excitation table of JK flip flop.

- 6. How many decade counters are required to convert a clock of 10 MHz to 100Hz.

| 1 | 2 | 1 |

|---|---|---|

| ( |   | ) |

| • |   | , |

- 7. What are the differences between RAM and ROM?

- 8. Write down two limitations of 1C.

Answer any *four* of the following:  $5\times4=20$

- 9. (a) Implement the following expression using NAND logic  $B\overline{C} + A + D$ .

- (b) Design Ex-OR gate using 4 NAND gate only. 5

- Minimize the following expression using K-Map:

F(A,B,C,D)-∏M(0,2,4,6,8,10,12,15)∏d(9,14)

d represents don't care.

- 11. A binary ripple counter is required to count up to (16,383)<sub>10</sub>. How many FFs are required? If the clock frequency is 8.192 MHz, what is the frequency at the output of the MSB? Determine the required number of flip flops for MOD-72 and MOD-148 counters.

- 12. A certain memory has capacity of 8KX16. How many data input and data output lines does it have? How many address lines does it have? What is the capacity in bytes?

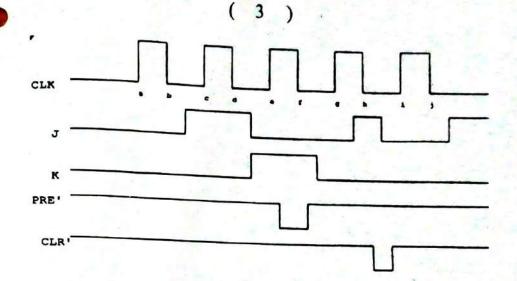

- 13. The input signals shown in figure below are applied to a positive edge triggered J-K flip flop with active low preset (PRE') and clear (GLR'). Draw the output waveform.

Subtract 1010 from 1101 using parallel adder IC 7483

(pin diagram not necessary).

Answer any *one* of the following:  $10 \times 1 = 10$

15. Write down the truth table of Half subtractor and determine the output expressions in SOP form the truth table. Design it using NAND gate only. Design 4:1 Multiplexer. How can you design 5:32 line decoder by cascading two 4:16 line decoder IC74154.

2+1+2+3+2

16. Explain the details operation of a stable multivibrator using IC555 timer. Derive the expression of frequency of generated wave. Determine its duty cycle. How can you modify the circuit for 50% duty cycle?

4+3+2+1